Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Project1:And Gate: Experiment

Cargado por

Santanu NathTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Project1:And Gate: Experiment

Cargado por

Santanu NathCopyright:

Formatos disponibles

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

PROJECT1:AND GATE

----------------------------------------------------------------------------------- Company: DBCET

-- Engineer: Santanu Nath

-- ID:DC2011BTE0059

-- Create Date: 21:46:50 01/20/2014

-- Module Name: andgate- Behavioral

---------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity andgate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : out STD_LOGIC);

end andgate;

architecture Behavioral of andgate is

begin

process (A,B)

begin

C<=A and B;

end process;

end Behavioral;

SIMULATION O/P:

RTL SCHEMATIC:

TECHNOLOGY SCHEMATIC:

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

PROJECT2:NAND GATE

----------------------------------------------------------------------------------- Company: DBCET

-- Engineer: Santanu Nath

-- ID:DC2011BTE0059

-- Create Date: 21:47:58 01/20/2014

-- Module Name: nandgate- Behavioral

---------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity nandgate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : out STD_LOGIC);

End nandgate;

architecture Behavioral of nandgate is

begin

process (A,B)

begin

C<=A nand B;

end process;

end Behavioral;

SIMULATION O/P:

RTL SCHEMATIC:

TECHNOLOGY SCHEMATIC:

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

PROJECT3:OR GATE

----------------------------------------------------------------------------------- Company: DBCET

-- Engineer: Santanu Nath

-- ID:DC2011BTE0059

-- Create Date: 21:48:30 01/20/2014

-- Module Name: orgate- Behavioral

---------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity orgate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : out STD_LOGIC);

End orgate ;

architecture Behavioral of orgate is

begin

process (A,B)

begin

C<=A or B;

end process;

end Behavioral;

SIMULATION O/P:

RTL SCHEMATIC:

TECHNOLOGY SCHEMATIC:

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

PROJECT4:NOR GATE

----------------------------------------------------------------------------------- Company: DBCET

-- Engineer: Santanu Nath

-- ID:DC2011BTE0059

-- Create Date: 21:50:01 01/20/2014

-- Module Name: norgate- Behavioral

---------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity norgate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : out STD_LOGIC);

End norgate;

architecture Behavioral of norgate is

begin

process (A,B)

begin

C<=A nor B;

end process;

end Behavioral;

SIMULATION O/P:

RTL SCHEMATIC:

TECHNOLOGY SCHEMATIC:

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

PROJECT5:XOR GATE

----------------------------------------------------------------------------------- Company: DBCET

-- Engineer: Santanu Nath

-- ID:DC2011BTE0059

-- Create Date: 21:52:48 01/20/2014

-- Module Name: xorgate- Behavioral

---------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity xorgate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : out STD_LOGIC);

end xorgate;

architecture Behavioral of xorgate is

begin

process (A,B)

begin

C<=A xor B;

end process;

end Behavioral;

SIMULATION O/P:

RTL SCHEMATIC:

TECHNOLOGY SCHEMATIC:

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

PROJECT6:XNOR GATE

----------------------------------------------------------------------------------- Company: DBCET

-- Engineer: Santanu Nath

-- ID:DC2011BTE0059

-- Create Date: 21:52:22 01/20/2014

-- Module Name: xnorgate- Behavioral

---------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity xnorgate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : out STD_LOGIC);

end xnorgate;

architecture Behavioral of xnorgate is

begin

process (A,B)

begin

C<=A xnor B;

end process;

end Behavioral;

SIMULATION O/P:

RTL SCHEMATIC:

TECHNOLOGY SCHEMATIC:

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

PROJECT7: You go home every Sunday or holiday but if there is no exam.

----------------------------------------------------------------------------------- Company: DBCET

-- Engineer: Santanu Nath

-- ID:DC2011BTE0059

-- Create Date: 21:58:01 01/20/2014

-- Module Name: project7 - Behavioral

---------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity project7 is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : in STD_LOGIC;

Y : out STD_LOGIC);

end project7;

architecture Behavioral of project7 is

begin

process (A,B,C)

begin

Y<=A or (B and(not C));

end process;

end Behavioral;

SIMULATION O/P:

RTL SCHEMATIC:

TECHNOLOGY SCHEMATIC:

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

Project 8: Half Adder

----------------------------------------------------------------------------------- Company: DBCET

-- Engineer: Santanu Nath

-- ID:DC2011BTE0059

-- Create Date: 21:57:01 01/20/2014

-- Module Name: halfadder- Behavioral

--------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity halfadder is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

S : out STD_LOGIC;

C : out STD_LOGIC);

end halfadder;

architecture Behavioral of halfadder is

begin

process(A,B)

begin

S<=(A xor B);

C<=(A and B);

end process;

end Behavioral;

SIMULATION O/P:

RTL SCHEMATIC:

TECHNOLOGY SCHEMATIC:

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

Project 8: Full Adder

----------------------------------------------------------------------------------- Company: DBCET

-- Engineer: Santanu Nath

-- ID:DC2011BTE0059

-- Create Date: 21:59:01 01/20/2014

-- Module Name: fulladder- Behavioral

---------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity fullader is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

Cin : in STD_LOGIC;

S : out STD_LOGIC;

C : out STD_LOGIC);

end fullader;

architecture Behavioral of fullader is

begin

process(A,B,Cin)

begin

S<=A xor B xor Cin;

C<=(A and B) or (B and Cin) or (a and Cin);

end process;

end Behavioral;

SIMULATION O/P:

RTL SCHEMATIC:

Experiment:......................................................................................... Expt. No. :...........................

Date: ...................................

............................................................................................................. Page No: ..............................

TECHNOLOGY SCHEMATIC:

También podría gustarte

- EDN Design Ideas 2003Documento165 páginasEDN Design Ideas 2003chag1956100% (2)

- Rslogix 5000Documento112 páginasRslogix 5000Richard Alejandro Riffo Arriagada0% (1)

- Solutions PDFDocumento161 páginasSolutions PDFSmriti Rai50% (2)

- Ecad & Vlsi LabDocumento98 páginasEcad & Vlsi LabbitseceAún no hay calificaciones

- Xilinx Lab RecordDocumento76 páginasXilinx Lab RecordDivya SantoshiAún no hay calificaciones

- Logic Design Lab Manual 10ESL38 3rd Sem 2013Documento61 páginasLogic Design Lab Manual 10ESL38 3rd Sem 2013vishvakirana75% (4)

- VHDL Testbench TutorialDocumento6 páginasVHDL Testbench TutorialJamesMatthewWongAún no hay calificaciones

- PIC Microcontroller Projects in C: Basic to AdvancedDe EverandPIC Microcontroller Projects in C: Basic to AdvancedCalificación: 5 de 5 estrellas5/5 (10)

- Implementing 802.11, 802.16, and 802.20 Wireless Networks: Planning, Troubleshooting, and OperationsDe EverandImplementing 802.11, 802.16, and 802.20 Wireless Networks: Planning, Troubleshooting, and OperationsCalificación: 4.5 de 5 estrellas4.5/5 (2)

- Timing PathsDocumento44 páginasTiming PathsMohammed El-Adawy100% (2)

- Operational AmplifierDocumento41 páginasOperational AmplifierAldino ManakoAún no hay calificaciones

- TDM Signals Simulation and RecoveryDocumento2 páginasTDM Signals Simulation and RecoverySantanu Nath75% (4)

- ECE 385 Fall 2014 Lab Manual 20140829Documento308 páginasECE 385 Fall 2014 Lab Manual 20140829x y0% (1)

- Visvesvaraya National Institute of Technology (VNIT), NagpurDocumento88 páginasVisvesvaraya National Institute of Technology (VNIT), Nagpurindiscon NagpurAún no hay calificaciones

- Computer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringDocumento71 páginasComputer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringSankhadeep ChakrabartiAún no hay calificaciones

- Laboratory ManualDocumento62 páginasLaboratory Manualتبارك موسى كريم علوانAún no hay calificaciones

- Template For Labs SoCDocumento3 páginasTemplate For Labs SoCTOSONAMiAún no hay calificaciones

- 4-Bit ALU Design in VerilogDocumento41 páginas4-Bit ALU Design in VerilogVenkata sai Prasad ChevuruAún no hay calificaciones

- CS6105-Digital Fundamentals and Computer Organization Laboratory Experiment ListDocumento4 páginasCS6105-Digital Fundamentals and Computer Organization Laboratory Experiment ListHistorian FamousAún no hay calificaciones

- Digital Circuits & Systems – II LabDocumento35 páginasDigital Circuits & Systems – II LabAbhinav RajAún no hay calificaciones

- Ece4750 Tut4 VerilogDocumento49 páginasEce4750 Tut4 VerilogSamAún no hay calificaciones

- Ecad and Vlsi Lab ManualDocumento125 páginasEcad and Vlsi Lab Manualsameer7mohammadAún no hay calificaciones

- VDF Project FinalDocumento109 páginasVDF Project Finalankit rajAún no hay calificaciones

- Writing Test Benches: A Free Application NoteDocumento8 páginasWriting Test Benches: A Free Application NoteEhsan MahdaviAún no hay calificaciones

- VLSI Record 6th Sem NIT TrichyDocumento67 páginasVLSI Record 6th Sem NIT TrichysumantaboseAún no hay calificaciones

- Dante Experiment#2Documento8 páginasDante Experiment#2CHRISTIANJOIE DANTEAún no hay calificaciones

- Index Page: S.No. Date Name of The Experiment Marks Awarded Remarks/ Initial's Part - ADocumento39 páginasIndex Page: S.No. Date Name of The Experiment Marks Awarded Remarks/ Initial's Part - ANaveenAún no hay calificaciones

- VHDL Lab ProgramsDocumento51 páginasVHDL Lab ProgramsvenkiAún no hay calificaciones

- Unknown 1Documento16 páginasUnknown 1Chetha SpAún no hay calificaciones

- FPGA Real Time Clock DesignDocumento12 páginasFPGA Real Time Clock DesignAL RIZWANAún no hay calificaciones

- Logic Gates and Full Adder Design in VerilogDocumento20 páginasLogic Gates and Full Adder Design in VerilogShahid241 alam100% (1)

- ENGG4420, REAL-Time Systems Design: Lab ManualDocumento46 páginasENGG4420, REAL-Time Systems Design: Lab ManualahmedAún no hay calificaciones

- Lab 11 ReportDocumento22 páginasLab 11 Reportnawinnawmu1026Aún no hay calificaciones

- Lab Manual: Submmitted byDocumento70 páginasLab Manual: Submmitted byMuhammad owais Muhammad munirAún no hay calificaciones

- University College of Engineering ArniDocumento51 páginasUniversity College of Engineering ArniVimalAún no hay calificaciones

- Lab ManualDocumento36 páginasLab ManualKeerthana SahadevanAún no hay calificaciones

- Ripple Carry Adder Aim:: Page 36 of 70Documento4 páginasRipple Carry Adder Aim:: Page 36 of 70Ganesh03071988Aún no hay calificaciones

- Vivekananda College of Engineering and Technology Puttur (D.K)Documento39 páginasVivekananda College of Engineering and Technology Puttur (D.K)Prince RajAún no hay calificaciones

- NandDocumento5 páginasNandrakeshkamasani123Aún no hay calificaciones

- BLACKlink Manual RDK Rev2 PDFDocumento269 páginasBLACKlink Manual RDK Rev2 PDFTommy AsselinAún no hay calificaciones

- Componentes Combinacionales en VHDLDocumento9 páginasComponentes Combinacionales en VHDLseb wood21Aún no hay calificaciones

- ECEN 248 Lab10 - ReportDocumento8 páginasECEN 248 Lab10 - ReportRebecca Sontheimer100% (3)

- Robotic Cell Project Progress ReportDocumento54 páginasRobotic Cell Project Progress Reportthanh_cdt01Aún no hay calificaciones

- Realize Logic Gates and Full Adder Using Verilog HDLDocumento18 páginasRealize Logic Gates and Full Adder Using Verilog HDLShahid241 alamAún no hay calificaciones

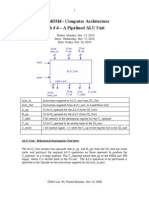

- ECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitDocumento8 páginasECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitsantoshmphilAún no hay calificaciones

- CoE 211 Digital Logic Design Lab Manual CoE v5Documento158 páginasCoE 211 Digital Logic Design Lab Manual CoE v5HanAún no hay calificaciones

- Experiment No: 1 HDL Code To Realize All The Logic Gates: Name: A.Vineela Reddy Date: HT N0.: 16H61A04C6 Page No.Documento49 páginasExperiment No: 1 HDL Code To Realize All The Logic Gates: Name: A.Vineela Reddy Date: HT N0.: 16H61A04C6 Page No.Suraj AnanthulaAún no hay calificaciones

- Lab 1 PresentationDocumento39 páginasLab 1 PresentationLê Đình TiếnAún no hay calificaciones

- Digital Logic DesignDocumento8 páginasDigital Logic DesignUsman UlHaqAún no hay calificaciones

- 15EC302J Vlsi Lab StudentsDocumento53 páginas15EC302J Vlsi Lab Studentshahemeb608Aún no hay calificaciones

- TIMER Radovan RabrenovicDocumento15 páginasTIMER Radovan RabrenovicRadovan RabrenovicAún no hay calificaciones

- Data Driven Clock Gating: Bar Ilan University School of Engineering Vlsi LabDocumento34 páginasData Driven Clock Gating: Bar Ilan University School of Engineering Vlsi LabaanbalanAún no hay calificaciones

- Lab: Initial Setup: 1. Create The Symbolic Link To The Lab Source DirectoryDocumento41 páginasLab: Initial Setup: 1. Create The Symbolic Link To The Lab Source DirectoryaanbalanAún no hay calificaciones

- 7th Sem VLSI Lab Manual Using Mentor GraphicsDocumento141 páginas7th Sem VLSI Lab Manual Using Mentor Graphicsvishvakirana50% (8)

- SystemC N BehaviorCoding Section2Documento110 páginasSystemC N BehaviorCoding Section2jasonturfAún no hay calificaciones

- HDL Lab Manual For VTU Syllabus (10ECL48)Documento64 páginasHDL Lab Manual For VTU Syllabus (10ECL48)Ravikiran B A100% (4)

- 36>?+@ 36>?A@ 36>?)@ 36Documento6 páginas36>?+@ 36>?A@ 36>?)@ 36Hai LúaAún no hay calificaciones

- TV Assig 5Documento8 páginasTV Assig 5ALL for WORLDAún no hay calificaciones

- DSD Lab Manuals: Design and Testing Onboard Switches and Led'S in FpgaDocumento4 páginasDSD Lab Manuals: Design and Testing Onboard Switches and Led'S in FpgaAL RIZWANAún no hay calificaciones

- Introduction To DSP TMS320F2812Documento18 páginasIntroduction To DSP TMS320F2812Pantech ProLabs India Pvt Ltd100% (1)

- Automated Test Rig For Electronic ProductsDocumento60 páginasAutomated Test Rig For Electronic ProductsraasisAún no hay calificaciones

- P.A College VLSI Lab Record 2012-13Documento50 páginasP.A College VLSI Lab Record 2012-13Sagar S Poojary100% (1)

- EEL4742-Lab-Manual-Embedded SystemsDocumento101 páginasEEL4742-Lab-Manual-Embedded SystemsSusie KAún no hay calificaciones

- VHDL programs for digital logic gatesDocumento33 páginasVHDL programs for digital logic gatesAnkit SharmaAún no hay calificaciones

- XYZ Acquisition System: Talha Ahmed Khan Ee-08-266 IMRAN SAEED EE-08-289Documento9 páginasXYZ Acquisition System: Talha Ahmed Khan Ee-08-266 IMRAN SAEED EE-08-289aloneheartsAún no hay calificaciones

- TDM 5Documento3 páginasTDM 5Santanu Nath100% (1)

- Application of ABCDDocumento15 páginasApplication of ABCDSantanu Nath50% (4)

- TDM Signal Multiplexing and Demultiplexing SimulationDocumento2 páginasTDM Signal Multiplexing and Demultiplexing SimulationSantanu NathAún no hay calificaciones

- Edc ReportDocumento5 páginasEdc ReportDebobrataAún no hay calificaciones

- MUX - StructuralDocumento2 páginasMUX - StructuralSantanu NathAún no hay calificaciones

- Noise Detector CircuitDocumento1 páginaNoise Detector CircuitSantanu NathAún no hay calificaciones

- Experiment: Project 19: Binary To Gray ConversionDocumento4 páginasExperiment: Project 19: Binary To Gray ConversionSantanu NathAún no hay calificaciones

- Mux 8Documento3 páginasMux 8Santanu NathAún no hay calificaciones

- Horn AntennaDocumento1 páginaHorn AntennaSantanu NathAún no hay calificaciones

- Demux Using XilinxDocumento3 páginasDemux Using XilinxSantanu NathAún no hay calificaciones

- Binary To GrayDocumento2 páginasBinary To GraySantanu NathAún no hay calificaciones

- SuperconductorDocumento27 páginasSuperconductorSantanu NathAún no hay calificaciones

- What Is An OrganizationDocumento8 páginasWhat Is An OrganizationSantanu NathAún no hay calificaciones

- Power Series Method For The Solution of Ordinary Differential EquationDocumento14 páginasPower Series Method For The Solution of Ordinary Differential EquationSantanu NathAún no hay calificaciones

- Q. Write A Program To Enter The Details of A Student Using Object Oriented Programming With C++Documento3 páginasQ. Write A Program To Enter The Details of A Student Using Object Oriented Programming With C++Santanu NathAún no hay calificaciones

- Object Oriented Programming With C++Documento5 páginasObject Oriented Programming With C++Santanu NathAún no hay calificaciones

- Charge Coupled Device1Documento5 páginasCharge Coupled Device1Santanu NathAún no hay calificaciones

- Resonance: University of The East - Caloocan College of EngineeringDocumento9 páginasResonance: University of The East - Caloocan College of EngineeringKim PambidAún no hay calificaciones

- ASD Assignment - IDocumento3 páginasASD Assignment - IAnkit AnandAún no hay calificaciones

- Low Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurDocumento27 páginasLow Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurHimaja DasariAún no hay calificaciones

- NTE74LS37 Integrated Circuit TTL Quad 2 Input Positive NAND BufferDocumento3 páginasNTE74LS37 Integrated Circuit TTL Quad 2 Input Positive NAND BufferElectronicos CaldasAún no hay calificaciones

- Introduction (KCL KVL)Documento14 páginasIntroduction (KCL KVL)etasureshAún no hay calificaciones

- LICA Ic NotesDocumento125 páginasLICA Ic Noteschandu3072002100% (1)

- REGENRATIVE - BRAKING - SYSTEM - Electrical (2) OkDocumento38 páginasREGENRATIVE - BRAKING - SYSTEM - Electrical (2) OkDeep ChoudharyAún no hay calificaciones

- MODULE 4 - Flip Flop & RegistersDocumento27 páginasMODULE 4 - Flip Flop & RegistersChaitanya J S ReddyAún no hay calificaciones

- Medi-Caps University: Digital ElectronicsDocumento54 páginasMedi-Caps University: Digital ElectronicsHarsh KumarAún no hay calificaciones

- MC10198 Monostable Multivibrator: CDIP-16 L Suffix CASE 620Documento12 páginasMC10198 Monostable Multivibrator: CDIP-16 L Suffix CASE 620MarceloCobaAún no hay calificaciones

- fvfssfDocumento5 páginasfvfssfztimmy0212Aún no hay calificaciones

- 0804Documento41 páginas0804Mehanathan Maggie MikeyAún no hay calificaciones

- Ucc 28880Documento41 páginasUcc 28880Cornel PislaruAún no hay calificaciones

- Assignment 1Documento3 páginasAssignment 1Degala Rajendra0% (1)

- 3 1 5 Ohms LawDocumento3 páginas3 1 5 Ohms Lawapi-291536660Aún no hay calificaciones

- Introduction to Biomedical Engineering course overviewDocumento18 páginasIntroduction to Biomedical Engineering course overviewSHADA ELWEFATIAún no hay calificaciones

- ExperimentDocumento9 páginasExperimentAgent PAún no hay calificaciones

- Itb-05c Linearisation of ThermocoupleDocumento20 páginasItb-05c Linearisation of Thermocouplekaushikei22Aún no hay calificaciones

- Microelectronics: Circuit Analysis and Design Donald A. NeamenDocumento11 páginasMicroelectronics: Circuit Analysis and Design Donald A. NeamenBhandari PrakashAún no hay calificaciones

- Types of Sources: Name: M. Sravya Sri Roll No.: 22R21A04A1 Branch& Sec: ECE-BDocumento9 páginasTypes of Sources: Name: M. Sravya Sri Roll No.: 22R21A04A1 Branch& Sec: ECE-BSAún no hay calificaciones

- Features: TL494 Pulse-Width-Modulation Control CircuitsDocumento18 páginasFeatures: TL494 Pulse-Width-Modulation Control CircuitsJeyakrishnan CAún no hay calificaciones

- Assignment-1: Attempt These Numericals 1Documento2 páginasAssignment-1: Attempt These Numericals 1prativaAún no hay calificaciones

- Hit SwitchDocumento1 páginaHit SwitchAsad AbbasAún no hay calificaciones

- John Errington's Tutorial On Power Supply Design: Constant Current and Current LimitingDocumento2 páginasJohn Errington's Tutorial On Power Supply Design: Constant Current and Current LimitingDai NgoAún no hay calificaciones

- Cpre 281: Digital Logic: Instructor: Alexander StoytchevDocumento63 páginasCpre 281: Digital Logic: Instructor: Alexander StoytchevFirman SitumeangAún no hay calificaciones