Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tesis: ATM Jesús Chávez Rodriguez: Esime Ipn

Tesis: ATM Jesús Chávez Rodriguez: Esime Ipn

Cargado por

Jota PiscoyaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tesis: ATM Jesús Chávez Rodriguez: Esime Ipn

Tesis: ATM Jesús Chávez Rodriguez: Esime Ipn

Cargado por

Jota PiscoyaCopyright:

Formatos disponibles

ATM

Captulo. 1

ESIME IPN

Tesis: ATM Jess Chvez Rodriguez

Marzo de 2002

ATM

Captulo. 1

1.1. CAPA FSICA ATM. La capa fsica se encuentra en el nivel ms bajo de la pila ATM. Esta toma las celdas llenas de la mitad de la capa y las transmite sobre el medio fsico. La ITUT originalmente defini solo dos velocidades las cuales pueden ser soportadas por ATM: 155.52 Mbit/s y 622.08 Mbit/s. De cualquier modo al finalizar el tiempo un nmero de velocidades adicionales e interfases se han desarrollado, que van tan bajo como E1 y tan alto como el rango de los Gbit/s. La misma capa fsica es subdividida en dos subcapas: La subcapa de convergencia de la transmisin (TC) y la subcapa dependiente del medio fsico (PMD). Estas dos subcapas trabajan conjuntamente para asegurar que la interfaz ya sea ptica o de cobre pueda recibir y transmitir las celdas eficientemente, con la apropiada estructura timing en lugar. ATM es una Tecnologa de Transmisin Internacional que ha sido capaz de trabajar con una variedad de formatos, velocidades, medios de transmisin y distancias que pudieran variar de pas a pas. La estandarizacin de las interfases habilitadas de la capa fsica asemeja tal conectividad: Modo-Fibra Simple, Fibra Multi-modo, Pares Coaxiales, y pares trenzados cubiertos y descubiertos estn todos estandarizados para el uso del ambiente ATM. LA subcapa de convergencia de la transmisin se encarga de revisar el encabezado de error (HEC) generacin y verificacin, empaquetamiento y desempaquetamiento de celdas, delineacin y desacoplamiento de celdas.

ATM

Captulo. 1

El HEC es un campo de 1 Byte en el encabezado de la celda ATM, el cul protege al encabezado de errores. En esta etapa los bits son ya reconocidos tal como vienen de la subcapa PMD. En esta subcapa se realizan bsicamente 5 funciones: 1.-Despus de la reconstruccin de los bits se hace la adaptacin al sistema de transmisin utilizado. Los sistemas pueden ser: Jerarqua Digital Sncrona (SDH Synchronous Digital Hierarchy). Jerarqua Digital Pleosncrona (PDH Plesiochronous Digital Hierarchy) o basada en clulas. Las clulas se fijan dentro del sistema de transmisin de acuerdo al mapeo estandarizado. 2.-Generacin del Chequeo de Error en Encabezado (HEC Header Error Check) para cada clula durante la transmisin y su verificacin en el receptor. Para comenzar, esto permite detectar las fronteras de la clula as como la delineacin apropiada de la clula en el receptor. 3.-Delineacin de la clula basado en el algoritmo delineador HEC, el cual asume que si el HEC es reconocido para un nmero consecutivo de clulas entonces se ha encontrado la frontera correcta de la clula. 4.-Una vez que la delineacin se ha localizado, se aplica un mtodo adaptativo, que usando el HEC, detecta y corrige errores en el encabezado dependiendo de la situacin.

ATM

Captulo. 1

5.-Finalmente esta subcapa debe asegurar la insercin y supresin de clulas sin asignar para adaptar el rgimen utilizable a la carga til del sistema de transmisin. Esta funcin se llama desacoplamiento del rgimen de clulas. La subcapa dependiente del medio fsico es responsable de la transmisin y recepcin correcta de bits en el medio fsico apropiado. En el ms bajo nivel de esta capa esta funcin es completamente dependiente del medio (ptico, elctrico, etc.) y es llamada Dependiente del Medio Fsico (PMD Physical Mdium Dependent). Adicionalmente, esta subcapa debe garantizar una apropiada reconstruccin del bit timing en el receptor. Por lo tanto la entidad al punto de transmisin ser responsable de insertar la informacin requerida de bit timing y codificacin de lnea.

Fig. 1.1. Capa Fsica ATM.

ATM

Captulo. 1

1.2. REFERENCIAS DE LA INTERFASE ATM. El diagrama mostrado en la figura 2, es crucialmente importante, este define la localizacin de todas las referencias de interfase en redes ATM. UNI-Privada: El usuario privado a interfase de red es la interfase entre un usuario final y un switch privado ATM. UNI-Pblico: Este es la interfase entre un usuario final y un switch publico ATM. Note que en esta definicin la red pblica se refiere a redes privadas como un usuario final y la red privada es el usuario final de el UNI. NNI-Pblico: La interfase pblica red a red es el ncleo de la ITU. El problema ms considerable aqu es la falta de definicin clara de un estndar de sealizacin entre switches portadores pblicos. UNI: Define todas las caractersticas de interfase (fsicas, elctricas, pticas, administracin y estructuras de datos) entre una terminal y el primer switch ATM en un sistema. P-NNI: Esta describe los procedimientos y protocolos a ser usados entre switches privados. El mecanismo de sealizacin aqu es derivado de la sealizacin UNI, por lo tanto P-NNI no daa los estndares de dficit experimentados en la pblica NNI.

ATM

Captulo. 1

NNI: Especfica como los switches estn siendo conectados juntos. Incluidos aqu estn algunos elementos de sealizacin inter-switch, el cul es necesario para que los switches ATM sean capaces de encontrar rutas a travs de largos sistemas complejos. B-ICI: La interfase del Ancho de Banda inter-carrier (B-ICI), como su nombre lo indica, es una interfase entre dos redes portadoras. Las recomendaciones proveen una rfaga de trabajo para la definicin de servicio hand-over de portadora a portadora. Un ejemplo aqu puede ser como la portadora de trfico SMDS sobre una red ATM de una portadora a otra es liberada a una red distante SMDS. Una consideracin similar puede darse a el hand-over del trfico Frame Relay. AINI: La interfase ATM Inter-Network (AINI) es un documento de progreso en el trabajo de entrada desarrollado con la intencin de definir la interfase entre sistemas autnomos. La palabra autnomo se refiere a redes que utilizan otras redes pero no desean saber los detalles de las otras implementaciones de definicin de AINI. redes. La B-ICI puede considerarse como un ejemplo de una AINI. Esta es una gran idea de trabajo a ser realizada en la

ATM

Captulo. 1

Fig. 1.2. Referencias de Interfase ATM.

1.3. LA INTERFASE FSICA SOPORTADA. Los documentos UNI muestran los medios fsicos permitidos en la interfase de usuario. Los detalles difieren para las UNIs publicas y privadas. Por ejemplo, el par trenzado categora 5 es permitido en la UNI privada pero no en la UNI pblica. El objetivo original para la Capa Fsica fue operacin sobre la Jerarqua Digital Sncrona (SDH) o Red ptica Sncrona (SONET) solamente.

ATM

Captulo. 1

De cualquier modo cuando las especificaciones del Foro ATM V3.0 y V3.1 fueron ratificadas, otras interfases fueron incluidas. Estas interfases fueron las DS3 y una interfase 100 Mbit/s basada en la interfase Transmisora/Receptora Asncrona Transparente (TAXI) Transparent Asynchronous Transmitter/Receiver Interface, y la interfase de datos distribuidos por fibra (FDI) Fibre Distributed Data Interface estndar. DS1 opera en 1.544 Mbit/s y es aprobado por ATM sobre par trenzado en distancias de arriba de 3000 pies. DS3 opera en 44.736 Mbit/s en cable coaxial arriba de 900 pies. STS-1 (51.84 Mbit/s), STS-3c (155.52 Mbit/s) y STS-12 (622.08 Mbit/s) opera sobre fibra en single-mode arriba de 15 km. E1 (2.048 Mbit/s) y E3 (34.368 Mbit/s), junto con el estndar Japons J2 (6.312 Mbit/s), son estandarizados para cable coaxial con una distancia no especificada. Recientemente una definicin para una interfase fsica de 2.5 Gbit/s (una interfase SDH) fue completada. Esta definicin describe como las celdas son mapeadas y transportadas a altas velocidades. El foro ATM regularmente en una especificacin de interfase de 10 Gbit/s.

ATM

Captulo. 1

Fig. 1.3. Interfases Fsicas Soportadas.

1.4. SDH/SONET. La Jerarqua Digital Sncrona y su similar Americano Red ptica Sncrona (SONET) forman el sistema de entrega de byte bsico de B-ISDN y por lo tanto para ATM. Estos sistemas de transmisin fueron diseados como sistemas multiplexores de gota sumador (MUX) para operadores y el formato de lnea contiene bytes administrados significativos a la calidad de lnea del monitor y uso. SDH y SONET estn gradualmente reemplazando a el viejo sistema de Jerarqua Digital Plesncrona (PDH). Los sistemas PDH han sido principalmente usados en la conmutacin telefnica y requieren de grandes espacios para acomodarlos.

ATM

Captulo. 1

Una ventaja de SDH es el pequeo pie de impresin de los gabinetes equipados, llevando a construirlos a bajos costos, menos generacin de calor y un mantenimiento mucho ms barato. Las ventajas de un ms alto ancho de banda, gran flexibilidad y escalabilidad hacen que estos sistemas sean ideales para ATM.

1.4.1. SDH y SONET. Como su nombre lo indica, SDH es un sistema de multiplexacin sncrono de un byte, pero adems tiene que soportar el transporte del canal de datos plesncrono. Este servicio a sido incluido en SDH primeramente, en velocidades bajas (arriba de 155.52 Mbit/s) SDH y SONET son diferentes; con SONET previendo la ms grande granularidad (velocidades debajo de 51.84 Mbit/s). Y en la cima 155.52 Mbit/s los rangos son los mismos. SONET y SDH, de cualquier modo no son inter-operables, debido a que ellos usan bits indicadores de control y alarma en diferentes maneras. Estas diferencias no son severas de cualquier modo y son fcilmente reconciliadas.

10

ATM

Captulo. 1

SDH / SONET El estndar bsico definido para soportar ATM es: -Estndar Europeo Jerarqua Digital Sincrona (SDH) -Estndar Americano Red ptica Sincrona (SONET) Los dos sistemas son idnticos en velocidades de transmisin de 155 Mbit/s y ms.

Fig. 1.4. SDH/SONET.

1.5. TOPOLOGA SDH. Una red SDH hace uso de anillos de fibra duales contra-rotating. Los

multiplexores son colocados alrededor del anillo para adicionar informacin. Estos multiplexores son conocidos como Multiplexores Sumadores a Gotas (ADMs) y ellos reemplazan todos los acumuladores de los multiplexores PDH a los cuales se hicieron referencia al principio. El ADM puede aceptar un amplio rango de velocidades de datos de entrada y servicios, incluyendo ISDN, ATM, FDI y LAN. Todas las velocidades PDH pueden ser intercaladas. En la ms alta velocidad del lado agregado, SDH transmite en tres velocidades las cules son de 155 Mbit/s, 622 Mbit/s y 2.4 Gbit/s.

11

ATM

Captulo. 1

Un simple ADM sncrono tal que tenga un amplio rango de interfases, puede proveer accesos a abastecimientos para una variedad de necesidades 1.544 Mbit/s, 2.048 Mbit/s, 34 Mbit/s, y ms. Altas velocidades de transmisin pueden ser acomodadas por multiplexores de altas velocidades. La interfase ptica de el ADM puede ser duplicada para proteccin esto es normalmente hecho para proveer al anillo dual contra-rotating operar en el modo este-oeste, con deteccin automtica de prdidas de seal y anillo de auto-mantenimiento. Esto incrementa la flexibilidad, ayudando a conservar los costos bajos de las redes.

Fig. 1.5. Topologa SONET/SDH.

12

ATM

Captulo. 1

Con SDH y SONET es usual para desplegar dos anillos de fibra separados el cul es conocido como Topologa de Anillo de Proteccin Dual. En esta configuracin el anillo secundario es utilizado para proveer redundancia. En el caso de una falla de cableado, el trfico puede ser direccionado al anillo de proteccin. El tiempo de ejecucin de este cambio es del orden de 20-40 ms. A menudo un simple anillo de repuesto es usado para facilitar la proteccin de un gran nmero de anillos trabajando. Los bits mas significativos en la estructura de la rfaga son usados para activar los procesos de conmutacin. Usando estos mtodos permiten al sistema de transmisin SONET/SDH la ejecucin de muy altos niveles de confiabilidad cuando el sistema desplegado en un ambiente local (cuando atraviesa un equipamiento de acumulador), con cableado punto-a-punto es el normal.

1.6. RFAGA SDH. SDH y SONET son sncronos con octetos alineados y sistemas de transmisin basados en rfagas. Todos los equipamientos en una red SONET/SDH comparten un reloj comn (atmico) el cual hace referencia a la Fuente de Referencia Primaria (PRS Primary Reference Source). En el caso de una falla en la distribucin del reloj, otro reloj local generar el timing. Cuando demasiados canales de trfico son multiplexados juntos, octetos (no bits) de cada una de las fuentes son intercalados.

13

ATM

Captulo. 1

Toda la transmisin en Sistemas SONET/SDH se realiza en rfagas discretas. Las rfagas son localizadas por un modelo de rfagas y todas las rfagas (independientemente de su tamao) son transmitidas en 125 micro segundos. Estos 125 micro segundos traiciona el origen de la telefona de SONET y SDH. La rfaga misma tiene una relativa importancia. El rea superior se encuentra en tres partes como se muestra en la figura 6 , consta de una seccin de repeticin, una seccin de lnea y una seccin de ruta. Estos trminos estn relacionados directamente a la figura previa. Seccin Repetidora (Section Repeater): Informacin intercambiada entre repetidores. La informacin incluye un valor de paridad para la rfaga previa y para un canal de voz, frecuentemente mencionada como el flujo F1. Seccin Multiplexora (Section Multiplexer): Informacin intercambiada entre dos multiplexores, tambin inclure revisiones de paridad y otros desempeos, tales como monitoreo e indicadores de alarma, comnmente mencionada como el flujo F2. Ruta (Path): Monitoreo remoto y control y control de informacin entre los puntos de entrada/salida de la red SONET/SDH. Esta puede ser la interfase fsica en el equipo del cliente. Esta es normalmente conocida como el flujo F3.

14

ATM

Captulo. 1

Carga til (Payload): Como su nombre lo indica, en esta es donde encontramos el trfico de usuario. En el caso de la transferencia de celdas ATM, muchos de los detalles de la estructura de la carga til pueden ser ignorados: en ATM definimos dos flujos ms F (4 y 5) que se encargan de el monitoreo entre puntos terminales (end-points). Estos puntos terminales son terminales de canales y rutas. Estos flujos se encuentran en forma de celdas inyectadas dentro del flujo de celdas del usuario. Adems una cosa en particular de la capa de adaptacin ATM, AAL2 define dos flujos ms F, F6 y F7. Esta es una caracterstica importante de ATM que puede usar un grupo consistente de operacin y mantenimiento principales (los F flujos) por toda la red, de un grupo de equipos de cliente a otro, monitoreando cada nivel. Puntero (Pointer): El puntero es usado para ajustar el tiempo de emisin de la carga til SDH con el fin de corregir las diferencias de reloj entre la red SDH y la fuente. Este procedimiento permite un llenado (filler) extra de octetos a ser insertados dentro del canal de bits en el caso de una seal tributaria baja. Esto adems permite capacidad extra para utilizarse en el caso de que la seal tributaria corra en algunos casos rpido.

15

ATM

Captulo. 1

Fig. 1.6. Rfagas SONET/SDH.

1.7. MAPEO DE CELDAS A RFAGAS. SDH y SONET presentan un mecanismo complejo para mapear diversos tipos de trfico a una rfaga de transporte de larga duracin y altas velocidades. Este trfico puede incluir estructuras de la Jerarqua Plesncrona: FDI, DQDB y ATM. El rea de carga til de una rfaga SONET/SDH no es exactamente divisible por 53 (el tamao de la celda) y de cualquier forma en la mayora de los casos una celda une dos rfagas. Cuando celdas son mapeadas a la carga til, estas son mapeadas una detrs de otra back-to-back esto es, que no delimitan al octeto a identificar el comienzo de una celda.

16

ATM

Captulo. 1

En definiciones anteriores de la interrelacin entre SONET y ATM, un mecanismo fue definido por donde un octeto con ndice de ruta superior (llamado H4) puede ser usado para identificar el lmite de la primera celda despus de lo ocurrido en el octeto H4. Este mecanismo cae dentro del desuso cuando este fue sealado fuera, estas estructuras correspondientes, no existen ms all de los 155.52 Mbit/s. El mecanismo nunca fue definido plenamente para implementacin en sistemas SDH. Esto presenta un problema, dado que SONET y SDH son octetos alineados (que es el identificador de limites de octetos de la subcapa PMD) y la capa ATM espera para recibir celdas de la capa fsica,, como son descubiertos los limites de las celdas.

17

ATM

Captulo. 1

Fig. 1.7. Mapeo de Celdas a Rfagas.

1.8. DELINEACIN DE CELDAS. Muchos Sistemas de Transmisin que estn calificados para usarse con ATM tienen en construccin mecanismos para delimitar fronteras entre las celdas. FDI y el Canal de Fibra usan un smbolo especial que no puede usarse en el flujo de trfico de usuario. DS-1, DS-3, E-3, etc; pueden usar una estructura de rfaga intermedia que es una celda alineada, refirindose a el como PLCP (Physical Layer Convergence Procedure). PLCP fue desarrollado de las tecnologas SMDS/DQDB.

18

ATM

Captulo. 1

El proceso de delineacin tiene dos formas que funcionan de la misma manera. En transmisin no-rfagas, el proceso es por alineacin de bits (bit aligned), mientras que en un sistema basado en rfagas tal como SDH o SONET, un proceso de octeto alineado (octet aligned) es ms apropiado. Con referencia a la figura 8, comenzaremos con el estado de cacera hunt. En este estado usamos la fuerza bruta para localizar cualquier celda. El mtodo es para calcular el valor HEC aleatoriamente eligiendo secuencias de 5 bytes (suponemos que esto es un encabezado). Si esta prueba falla entonces trataremos con los siguientes cinco. Dado que estos encabezados tienen una longitud de 5 bytes y las celdas una longitud de 53 bytes, nosotros nos limitaremos a encontrar un encabezado. Recordar que puede coincidentemente ser correcto cul no es encabezado; en este caso nosotros esperaremos 48 bytes y lo intentaremos otra vez. Despus del primer clculo correcto nos moveremos al estado Presncrono donde nuevamente esperaremos 48 bytes, cuando el proceso de espera e intentar de nuevo nos resulta correcto (HEC supervisa correctamente) seis veces seguidas, entonces se puede decir que se encuentra en sincrona y hace la transicin al estado de sincrona donde pasamos a identificar ahora celdas de la capa ATM.

19

ATM

Captulo. 1

Fig. 1.8. Delineacin de Celdas.

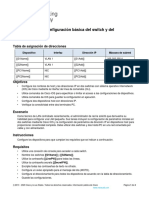

1.9. SDH/SONET ACRNIMO. La tabla mostrada, lista el acrnimo comnmente usado cuando nos referimos al SDH Europeo y al Sistema SONET Americano. STM-N es Mdulo de Transporte Sncrono de nivel N. STS es Seal de Transporte Sncrona de nivel N. OC-N es Canal o Portador ptico de nivel N.

20

ATM

Captulo. 1

Como anteriormente se mencion, note que este es granularmente ms grande en la Jerarqua SONET que en la SDH.

Fig. 1.9. Acrnimo SDH/SONET.

21

ATM

Captulo. 1

1.10. LA IMPLEMENTACIN FSICA DE SDH. Aunque los Sistemas Portadores e Interfases pticas son preferidos para transportar las celdas ATM debido a sus inherentes bajos errores de velocidad, otras interfases son especificadas. Fibra es la conexin preferida para las compaas de Telegrafa y Telefona (PTT); interfases sobre conexiones WAN y MAN usando altas ejecuciones, modo de fibra simple y servicios lser; y para distribucin alrededor de sitios de campo y edificios usan el estndar industrial 62.5/125 m de fibra multi-modo. La Categora 5 de Par Trenzado sin Blindaje (UTP) es muy bien aceptada por los circuitos de cola ATM, liberando ATM a las estaciones de trabajo y para servicios tales como cdigos de videoconferencia. La implementacin de LAN en ATM es portada usando una combinacin de velocidades y medios.

1.10.1. MEDIOS UTILIZABLES. Aunque la Categora 5 UTP es preferida para distribucin local ATM, la Categora 3 UTP a sido probada, adems la Categora 3 a sido encontrada satisfactoria para velocidades terminales bajas y distancias cortas. De cualquier modo si UTP es usado, entonces toda la planta cableada incluyendo punchdowns y wall-face plates deben ser cableados de la misma forma .

22

ATM

Captulo. 1

La Asociacin de Industrias Electrnicas (EIA) provee un estndar conocido como 568A. Este estndar requiere de un cableado terminal-terminal (end-toend) en UTP categora 5 podra ser no mayor que 100 m, con 90 m reservados para el horizontal y 10 m combinados para el cordn parchado.

Implementacin Fsica SDH Aspectos Fsicos de SDH / SONET -Fibra Modo Simple -Conexin preferente para su operacin Multi-modo -Usada para redes Privadas ATM, por ejemplo Universidades -UTP Categora 5 -Usada entre Grupos de Trabajo -Para reemplazar LANs tradicionales con ATM

Fig. 1.10. Implementacin Fsica de SDH.

23

ATM

Captulo. 1

2.1. CAPA ATM. La capa ATM describe diversos fundamentos de ATM tales como la estructura de las celdas adems de uso de rutas virtuales y canales. Las celdas llenadas en esta capa son transportadas a la capa fsica para transmisin.

2.1.1. SERVICIOS DE LA CAPA ATM. La capa ATM se encarga del suministro de circuitos virtuales para la transferencia de la Unidad de Datos de Servicio (SDUs) sobre una interfase UNI o NNI. Una Unidad de Datos de Servicio (SDU) consta de 53 octetos de longitud. La estructura de esta celda depende de si esta tiene que pasar entre un sistema terminal y un switch ATM o entre switches. Las conexiones son levantadas a travs de ATM usando circuitos virtuales predefinidos para establecer las conexiones punto a punto. La calidad del servicio suministrado a el usuario-terminal es especificada en un contrato de trfico entre el usuario y la red. El mismo contrato de trfico especificar un nmero de artculos incluyendo el ancho de banda a ser ocupado en las direcciones de avanzado o retroceso, la capa de adaptacin especfica a ser usada, la calidad de servicio (QoS) requerida y diversos parmetros de trfico.

24

ATM

Captulo. 1

Fig. 2.1. Capa ATM.

2.2. ENCABEZADO DE CELDA UNI. El contenido carga til de una celda ATM es siempre de 48 bytes, si se est usando una interfase UNI NNI. Estas son pequeas diferencias entre los encabezados de celda UNI y NNI: El encabezado de celda UNI contiene un Campo de Control de Flujo Genrico (GFC) el cul no se encuentra definido y por lo tanto no es usado. Formato de celda de una Interfase Usuario-Red:

Control de Flujo Genrico (GFC). Identificador de Ruta Virtual (VPI). Identificador de Canal Virtual (VCI). Identificador del Tipo de Contenido o Carga til (PTI).

25

ATM

Captulo. 1

Prioridad de Celda Prdida (CLP). Correccin de Error de Encabezado (HEC).

Fig. 2.2. Encabezado de Celda UNI.

2.3. ENCABEZADO DE CELDA NNI. El Foro ATM para un encabezado de celda de una Interfase NNI, elimina los cuatro bits del campo de Control de Flujo Genrico, permitiendo un mayor rango de Rutas Virtuales a ser soportadas. Identificador de Ruta Virtual (VPI). Identificador de Canal Virtual (VCI). Identificador del Tipo de Contenido Carga til (PTI).

26

ATM

Captulo. 1

Prioridad de Celda Prdida (CLP). Correccin de Error de Encabezado (HEC).

Una conexin terminal-a-terminal en ATM es algunas veces conocida como una Conexin de Canal Virtual (VCC), y consiste del nmero de Rutas y Canales Virtuales:

VCC = VPI + VCI

Fig. 2.3. Encabezado de Celda NNI.

27

ATM

Captulo. 1

2.4. CONTROL DE FLUJO GENRICO.

El Campo de Control de Flujo Genrico fue sumado a la insistencia de Bellcore en 1988 cuando fue originalmente pensado para brindar mltiples servicios ATM en una Interfase UNI. De cualquier modo es poco probable que esta funcin sea siempre implementada. Para esta Funcin han sido diseados dos modos de operacin: acceso sin control y acceso controlado.

Para equipos que usan el acceso sin control, el campo de Control de Flujo Genrico (GFC) no es utilizado y los bits son siempre puestos en 0000 binario para transmitir celdas. Para equipos que usan el modo de acceso controlado, la definicin actual de este campo (GFC) no es an acordada.

Esto es de cualquier modo una definicin para el uso del campo de Control de Flujo Genrico: S un servicio recibe 10 (diferente de cero) campos GFC dentro de los 1000-30000, celdas recibidas, este considera el otro servicio ATM usando modo de acceso controlado y notifica su capa como funcin de administracin.

28

ATM

Captulo. 1

Control de Flujo Genrico Solo empleadas de manera local en UNI -Ningn valor puede ser sobrescrito por el switch. Dos modos de operacin: -Modo Controlado -Modo No controlado

Solo el modo No-controlado se encuentra definido

-No controlado GFC=0000

Fig. 2.4. Control de Flujo Genrico.

2.5. IDENTIFICADOR DE RUTA VIRTUAL (VPI).

ATM es un protocolo orientado a conexin el cul necesita las direcciones de estacin-terminal slo una vez, en el tiempo de un levantamiento de llamada;

29

ATM

Captulo. 1

despus de esto la direccin ATM ya no es requerida tal que el sistema slo necesita anexar a la celda un recordatorio (notificacin) de cul conversacin voz, datos video- pertenece la celda. Esta notificacin en la forma de la combinacin VPI/VCI, es usada por la tabla look-up (mejoramiento) en cada switch ATM, a travs del cul las celdas viajan para asegurar una conmutacin de celdas precisas entre el puerto de entrada y el puerto de salida.

El Identificador de Ruta Virtual (VPI) tiene 8 bits disponibles en la interfase UNI y 12 en la NNI, dando uno u otro 256 4096 VPs simultneos sobre los cules los datos viajarn en canales virtuales (VCs).

Es normal en implementaciones privadas ATM usar una simple ruta virtual (VPI=0), visto que los operadores hacen uso extensivo de VPIs para simplificar la conmutacin de nmeros muy grandes en VCs los cules viajan dentro de una ruta.

2.5.1. RUTAS VIRTUALES (OVERVIEW).

Los valores para el VPI y el VCI son nicos para especificar enlaces entre dos sitios ATM. Los valores pueden cambiar cuando la ruta atraviesa un switch, pero esto no presenta un problema desde que el switch maneja conexin-cruz (hbrida) de una combinacin de VPI/VCI en un enlace a una combinacin VPI/VCI a el siguiente enlace.

30

ATM

Captulo. 1

Pero porqu ambos VPI y VCI y no slo un amplio rango de VCIs? El concepto de ruta virtual originado concierne al costo de controlacin de redes B-ISDN. La idea fue agrupar un nmero de conexiones compartiendo una ruta comn a travs de la red dentro unidades identificables (paths).

Acciones de administracin de red pueden ser aplicadas en pequeos grupos de conexiones en vez de grandes nmeros de conexiones individuales. Por ejemplo, un cliente puede tomar un servicio ATM de una portadora para conectar varios sistemas de computadoras de usuarios a un servidor. En caso de un desastre la recuperacin consistir en un redireccionamiento de la ruta virtual en vez de redireccionar individualmente cada canal.

Identificador de Ruta Virtual Identifica la Ruta de la Celda 8 bits disponibles en la UNI 12 bits disponibles en la NNI -256/4096 rutas simultneas posibles -Un nmero mximo de bits utilizables es negociable entre el usuario y la red

Fig. 2.5. Identificador de Ruta Virtual.

31

ATM

Captulo. 1

2.6. IDENTIFICADOR DE CANAL VIRTUAL (VCI).

Cada celda la cul es originada de un servidor ATM y la cul es destinada para un servidor remoto ATM debe identificarse a travs del sistema; la celda por lo tanto porta un nmero nico de CVI en el encabezado.

Este nmero es uno a uno asignado por el administrador de la red en el caso de una conexin permanente terminal-a-terminal (PVC), o es elegida por el switch ATM en el caso de un levantamiento de una llamada por seleccin de un no asignado equipo de VCIs, en el caso de una conexin conmutada (SVC).

La VCI es nica para ambos puertos y rutas un VCI en la salida de un switch no tiene que soportar los mismos parmetros que un VCI de 100 en la entrada de el mismo puerto. Los canales virtuales pueden ser unidireccionales, poco comn en los circuitos telefnicos donde las llamadas son siempre levantadas de manera bidireccional. Para establecer una llamada bidireccional el levantamiento necesitar especificar el ancho de banda requerido en la direccin de regreso.

32

ATM

Captulo. 1

Los identificadores de circuitos virtuales pueden ser re-mapeados cuando transmiten a travs de un switch, esta es una funcin estndar. Si este es el caso, el HEC (Correccin de Error en el Encabezado) es vuelto a calcular cada vez. El tamao del campo VCI dos bytes- permitidos para un total de 65535 VCIs.

2.6.1. CANALES VIRTUALES.

El enlace fsico ATM porta celdas que pueden ser visualizadas tal como existen subdivididas en pequeas rutas, donde cada una contiene mltiples rutas a pequea escala. Esta manera de concebir los circuitos virtuales puede ayudarnos a entender como los operadores aplican el concepto de un VPI para habilitar grupos de circuitos que son fcilmente administrados.

El VPI puede ser transportado en un pequeo cable multi-ncleo dentro de un cable de mayor tamao, donde cada uno de los ncleos ser un VCI. Un canal puede portar muchos ms VPIs y si un lmite falla requerir el re-enrutamiento de VPIs estos pueden ser portados mucho ms fcilmente en el nivel VPI que en el nivel VCI.

En el nivel VPI es slo necesario liberar un comando para re-enrutar un VPI de la fuente a su destino y todos los VCIs viajando dentro; que VPI automticamente los conmutar como tal. Esto minimiza la carga de los mecanismo de control.

33

ATM

Captulo. 1

Identificador de Canal Virtual Identifica el Canal de la Celda 16 bits disponible en la NNI y UNI - 65,536 posibles canales simultneos por ruta - Un nmero mximo de bits utilizables es negociable en una ruta por base.

Fig. 2.6. Identificador de Canal Virtual.

2.7. RUTAS VIRTUALES.

Para crear un circuito virtual permanente a travs de la red, canales mltiples pueden ser asociados con esa ruta en una terminal.

34

ATM

Captulo. 1

Estos canales sern conmutados a travs de la red sobre la ruta sin tener que ser individualmente conmutados en cada switch intermedio ATM. La tcnica de ruta virtual guarda los tiempos y recursos dentro de estos switches.

Fig. 2.7. Rutas Virtuales.

2.8. CONEXIONES VIRTUALES RESERVADAS.

Las primeras 32 VCIs (0 a 31 decimal) son reservadas para especificar funciones y por lo tanto el primer VCI el cul es asignable a usuario es el VCI 32. La ITUT usa los primeros 16, y el Foro ATM le ha sido asignado el segundo grupo de 16.

35

ATM

Captulo. 1

Tcnicamente hablando, slo ciertos valores de VCI son reservados en VPIs particulares, por lo tanto para uso pblico se ha adoptado que valores de VCI de 0-31 sean reservados para todos los valores de VPI.

Dando un amplio rango de valores disponibles. Esto no es visto como un problema ya que simplifica la implementacin. Recientemente la combinacin VP 0 VC 32 fue reservada para MPLS (Multi Protocol Label Switching) control de trfico. Este canal reservado ser usado por switches que cuenten con el software de MPLS instalado. Esto difiere de los canales reservados (VCIs 0 a 31) en que 0 a 31 estn permanentemente reservados de acuerdo a cul software es instalado en el switch.

Fig. 2.8. Conexiones Virtuales Reservadas.

36

ATM

Captulo. 1

2.9. IDENTIFICADOR DEL TIPO DE CARGA TIL (PTI).

Un control de celdas usa los tres bits PTI y un bit de prioridad de celda perdida. El PTI define la informacin que es portada en la celda. Celdas con contenido de datos de usuario y administracin de redes son diferenciados.

El bit dos de el campo de tres bits puede ser usado para indicar congestin en el trfico de datos, aunque este no este todava plenamente definido. El bit uno es usado para indicar el final de la celda en una trama de celdas las cules han sido llenadas como empaquetamiento de trfico de alto nivel. Esto es usado para ayudar al switch a administrar la congestin de las celdas de cola de salida.

Recuerde que esto no es un flujo de control en ATM, adems las celdas continuarn llegando al switch, aunque este no pueda manejar la congestin consecuente. Si una cola de celda es congestionada en el punto donde necesariamente llega para empezar a descartar celdas, es mejor hacerlo descartando celdas de canales especficos que aleatoriamente. Si un grupo de celdas de un VCI especfico es marcado a la entrada como un camino que el switch conoce donde se encuentra, as como donde empieza y termina un grupo de celdas, entonces el switch puede descartar todas las celda de un grupo para reducir la congestin.

La alternativa es para descartar celdas aleatoriamente de canales de celdas mltiples; esto inevitablemente nos guiar a un incremento en la congestin

37

ATM

Captulo. 1

cuando la recepcin termine de reensamblar las celdas de datos dentro de paquetes de alto nivel, los revisar y descubrir que datos estn perdidos.

La retransmisin ser requerida por todos los canales los cuales detectarn datos perdidos, que guiaran a un punto mas lejano la congestin cuando la repeticin llegue al switch.

PTI MSB (bit 3). El bit ms significativo del campo PTI indica si la celda es una celda administradora (bit=1), o una celda de sealizacin/usuario. Si es una celda administradora entonces la codificacin en los siguientes dos bits es como sigue: S el bit dos y tres estn en uno entonces este es un cdigo reservado. Si estos mismos bits son diez, esta es una celda administradora de recursos. Los dos principales cdigos indican que la celda es una parte del flujo de celda F5 OAM. S el cdigo es 00, esto es F5 OAM en una base de segmento-por-segmento. S el cdigo es 01 el flujo es F5 OAM terminal-a-terminal.

PTI (bit 2). Este bit es un identificador de congestin y nosotros direccionaremos esto en una superficie separada.

PTI (bit 1). Este bit es llamado de diversas formas: bit de Unidad de datos de Servicio (SDU Service Data Unit), el bit (documentaciones anteriores). Su uso es para identificar el fin la ltima celda en una capa superior

38

ATM

Captulo. 1

(Protocol Unit Data) PDU cuando la capa de adaptacin 5 (AAL5) es usada .

Fig. 2.9. Identificador del Tipo de Carga til.

2.10. CONTROL DE CONGESTIN.

39

ATM

Captulo. 1

La Congestin ocurre en una red ATM cuando un recurso a sido sobre vendido, cuando una red falla a sido encontrada, o cuando celdas no logran conformar el contrato de trfico. Bajo circunstancias normales, la congestin no debera ocurrir porque un algoritmo de Control de Admisin en la Conexin (CAC) no lo permitir.

Un indicador de congestin avanzado explcito (EFCI) es un mecanismo de notificacin de congestin el cul el usuario terminal usa para mejorar la utilidad de la conexin.

Una celda transitando un rea de congestin puede poner el bit EFCI de el PTI para indicar el origen donde se encuentra el problema en alguna parte entre la fuente y el destino.

Esto entonces eleva el servicio terminal para implementar un protocolo con la finalidad de bajar la velocidad de conexin de la celda durante la congestin. Aunque EFCI es ampliamente implementada, el tiempo entre una emisin de una celda y el tiempo en el cul la fuente es notificada de esta congestin puede ser largo.

Periodo de Viaje Redondo (RTT Round Trip Time): Considera un caso extremo; s el RTT es de 0.5 segundos y la velocidad de interfase de la fuente es 40 Mbit/s, entonces 20 millones de bits sern enviados antes de que la congestin sea notificada a la fuente.

40

ATM

Captulo. 1

Descartado de Paquetes Tempranamente (EPD Early Packet Discard): Es un procedimiento que nos puede ayudar en caso de congestin. Si la congestin es establecida por una estacin terminal que usar la capa de adaptacin 5 (AAL5), entonces usa un bit en el encabezado que indica la ltima celda en un grupo de celdas pertenecientes a la capa superior PDU. Aqu hay dos tcnicas posibles: En el caso de que una celda sea removida o recortada, recorta el resto de las celdas anteriores a esta marcada como la ltima (deja que pase), o remueve un paquete entero de celdas inmediatamente despus de la celda marcada (ltima) incluyendo la siguiente celda marcada.

Buffers: Ambas tcnicas descritas arriba operan en el nivel del buffer en el switch. Si una celda es perdida en una condicin de congestionamiento, nosotros podemos conmutarla dentro del mecanismo EPD y descartar las celdas de los buffers. Usualmente el switch contiene un mecanismo de presin reversible que hace que las celdas sean descartadas en la interfase de salida a el switch. El proceso indicado aqu opera en el nivel de conexin.

41

ATM

Captulo. 1

Control de Congestin El Bit 2 del PTI puede ser usado para indicar el destino que la congestin ha tomado en la red. El bit es llamado Indicador de Avance de Congestin (EFCI). Esto ocurrir cuando los switches descarten las celdas con CLP=1.

Fig. 2.10. Control de Congestin.

2.11. PRIORIDAD DE PRDIDA DE CELDA (CLP).

42

ATM

Captulo. 1

Este campo de bit simple puede ser referido como la llave a la administracin del trfico interno ATM. El bit puede ser puesto por el equipo de la estacin terminal ATM pero limpiado por switches ATM. Esto puede ocurrir cuando los circuitos portadores fracasan, si el equipo de la estacin terminal ATM transmite en una velocidad ms alta que la especificada en el contrato de trfico.

Si el bit de Prioridad de Prdida de Celdas es usado, le permite a la red descartar la celda en el caso de que tenga un ancho de banda insuficiente para la correcta transmisin de la celda y todas las dems celdas que requirieran de un ancho de banda. El propsito de este bit es el de identificar celdas que pueda descartar antes que las celdas que no cuentan con este bit. Bajo condiciones normales la reservacin de ancho de banda podra necesitar de descartar algunas celdas, pero esto puede hacer que un usuario escogiera un CLP=1 para tomar ventajas de bajas tarifas para trfico. Trfico con CLP=0 normalmente ser tarificado en una velocidad alta.

2.11.1. OPERACIN DEL CLP.

Si una celda llega al switch con una velocidad de datos ms alta que la acordada en el contrato de trfico, el switch tiene la capacidad de cambiar el bit CLP colocando un indicador de que la celda puede ser descartada.

43

ATM

Captulo. 1

Esto no es apropiado para trfico en el que pasan ms altas velocidades de datos que las contratadas. El bit polica que se encarga de supervisar el trfico es el que decide cuales celdas deben ser puestas en prioridad baja o descartadas.

Prioridad de Celda Perdida CLP opera independientemente en cada VPI/VCI activo. Un switch puede enviar un CLP de 0 a 1, por ejemplo, si el trfico en un VPI/VCI excede una velocidad de celda mxima acordada.

Fig. 2.11. Prioridad de Celda Perdida.

2.12. CORRECCIN DE ERROR EN EL ENCABEZADO (HEC).

44

ATM

Captulo. 1

El contenido en portadoras ATM de deteccin de no error o mecanismos de correccin, dependen en cambio de circuitos portadores de baja velocidad de error, recibiendo terminales de software, recibiendo notificaciones de no terminacin por haber celdas perdidas.

Esta condicin slo aplica en conexiones de tiempo real de voz o video. Donde una pequea proporcin de celdas puede ir por un camino equivocado sin ser notificada.

La correccin de error en el encabezado (HEC) es utilizada para proteger el encabezado entero, incluyendo el HEC mismo. Este solo bit es capaz de hacer la funcin de deteccin y correccin tan bien como un bit de deteccin mltiple pero no correccin mltiple de bits. Si una celda es avanzada sin la correccin tomada en cuenta, no solo el destino correcto no recibir la celda podra llegar a otro destino con resultados impredecibles.

La fuente ATM calcula el error HEC basado en todos los cinco bytes incluyndose el mismo. El receptor y la otra terminal del enlace tienen dos modos de operacin: Modo de Deteccin y Modo de Correccin. El soporte de modo de correccin es opcional.

Cuando ocurren errores, ellos estn tpicamente caracterizados por uno u otro bit de error simple o relativamente grandes rfagas de errores:

45

ATM

Captulo. 1

En el caso de un bit de error simple, este ser corregido. El modo de operacin conmutara la deteccin. S el siguiente HEC es correcto, el modo de operacin regresa a la correccin. En el caso de una rfaga de errores, la primera celda afectada ser descartada. Las celdas siguiente y subsecuente pueden o no ser descartadas, dependiendo del tamao de la rfaga.

Correccin de Error en Encabezado. El HEC solamente es ejecutado en el encabezado. - Soporta correccin de avance de un bit de error simple. - Soporta deteccin de errores de bit mltiples. Fallas en celdas son descartadas. - En la UNI La deteccin de Error es obligatoria. La correccin de Error es opcional. El HEC es generado y verificado en la subcapa TC de la Capa Fsica.

Fig. 2.12. Correccin de Error en Encabezado.

2.13. CANALES Y RUTAS VIRTUALES.

46

ATM

Captulo. 1

Dentro de un nodo nosotros podemos elegir las decisiones de conmutacin base en los valores VPI/VCI como un par (VC Conmutado) o usar el valor VPI slo (VP Conexin Hbrida). En el caso de una conexin Hbrida VP, el switch puede conmutar un grupo de canales (todos ellos con el mismo VPI) a el mismo destino.

Esto puede ser una simplificacin en trminos de administracin de recursos y puede ser ms rpido. Para la ms grande funcionalidad, el switch usa el par combinado VPI/VCI. En este caso, canales individuales pueden ser enrutados.

Fig. 2.13a. Canales y Rutas Virtuales.

47

ATM

Captulo. 1

Los trminos que aqu conoceremos son Enlace de Canal Virtual (VCL), el cul es un simple salto a travs de una pieza de cable interfase-a-interfase, y una Conexin de Canal Virtual (VCC), la cul es una concatenacin de series terminal-a-terminal de enlaces VC. Recordar que los valores de VPI y VCI tienen solo un significado local y son capaces de cambiar en cada punto de conmutacin.

Fig. 2.13b. Canales y Rutas Virtuales.

48

ATM

Captulo. 1

2.14. EL SWITCH DE MAPEO.

Un switch de mapeo es encontrado en cada interfase (el nombre para esta estructura varia entre los diseadores) Las tablas son almacenadas en la estructura MIB y la forma de implementacin es enteramente distribuidorespecfico.

Este mapa contiene el mapeo entre los valores entrantes VPI y VCI y los nuevos valores para el siguiente mapeo. Adems encontramos una identificacin de el puerto de salida de este switch.

Los valores en el mapeo del switch son enteros por un proceso manual en el caso de una conexin virtual permanente, o desarrollados dinmicamente para un mecanismo de sealizacin.

La manera en la cul la interfase de salida es indicada, vara con la arquitectura del fabricante. En el caso de memoria compartida fbrica informacin delta

49

ATM

Captulo. 1

para cada uno de lo elementos de conmutacin intermediarios; este representado por una cola en memoria compartida asociada con el puerto de salida.

Fig. 2.14. El Switch de Mapeo.

50

ATM

Captulo. 1

3.1. CAPA DE ADAPTACIN. La capa de adaptacin se encuentra en el nivel ms alto en ATM. Esta es usada para adaptar el trfico de datos en un formato ATM (celdas); en otras palabras son empaquetadas dentro de celdas con una longitud de 48 bytes. La funcin de adaptacin es realizada en los limites de una conexin ATM y no dentro de la red. Existen diferentes Capas de Adaptacin dependiendo las necesidades del usuario (voz, video, grficos, etc), las cules han sido definidas por la ITU-T y el Foro ATM. La capa misma es dividida en su interior en dos sub-capas: Subcapa de Convergencia (CS). Subcapa de Segmentacin y Reensamblado (SAR).

Funcin de Adaptacin: No sera posible usar solo un estndar de capa de adaptacin en ATM para todos los tipos de datos existentes porque voz, video y datos tienen completamente caractersticas diferentes; ests caractersticas varan entre sncronos y asncronos, velocidades de bits variables o constantes, tiempo real y tiempo no-real. Adems necesita ser capaz de adaptar ATM (modo orientado a conexin), al trfico portador el cul opera en un modo no orientado a conexin en su forma original. Adems ATM fue diseada para ser capaz de manejar Datos de Frame Relay, los cules se encuentran en paquetes-conmutados y orientados a conexin.

51

ATM

Captulo. 1

Adems ATM debe ser capaz de acomodar los diversos requerimientos de asociacin de timings y prioridades de datos y asignar diferentes calidades de servicio a el trfico. Calidad de Servicio (QoS): Se refiere al mayor nmero de informacin transferida durante un enlace dividiendo datos dentro de cuatro clases separadas y asignndoles a cada una de ellas sus propios parmetros QoS simplificando el levantamiento de llamadas como el tipo de datos, asignndoles su propio QoS.

Fig. 3.1. Capa de Adaptacin.

52

ATM

Captulo. 1

3.2. CATEGORAS DE SERVICIO QOS.

QoS nos muestra las necesidades de el usuario para una aplicacin en particular, donde un nmero de categoras han sido definidos. Servicios de voz por ejemplo, requieren de un mnimo de retardo terminal-a-terminal para minimizar la necesidad de utilizar canceladores de eco. Aplicaciones de video no permiten perdida alguna de datos que resultara en una degradacin de imagen. Servicios de datos toleran ms los retardos as como variaciones en los mismos.

CBR: CBR ha sido definido para soportar velocidades de bit constantes, trfico orientado a conexin, donde la sincronizacin terminal-a-terminal es requerida. Esto es de otra manera conocido como requerimientos de ejecucin ITU-T Clase A. Este servicio puede conocer los requerimientos ms comunes para ejecucin comparables hoy a los servicios de lneas privadas digitales tal como un E1. VBR-RT: VBR-RT ha sido definido para soportar velocidades de bit variables, trfico orientado a conexin, donde la sincronizacin terminala-terminal es requerida. Esto es de otra manera conocido como requerimientos de ejecucin ITU-T Clase B. Este servicio es usado para empaquetar aplicaciones de voz y video, tales como sistemas de videoconferencia. VBR-NRT: VBR-NRT es utilizado para tipos de trfico los cules son predecibles, no requieren de un vnculo con el timing para mantener una conexin terminal-a-terminal. Este servicio puede ser utilizado para la interconexin en redes LAN.

53

ATM

Captulo. 1

ABR: El servicio ABR es diseado para brindar un soporte econmico de aplicaciones con requerimientos ambiguos para retardos. Aunque ABR es mencionado aqu, este no es especificado en UNI 3.0 3.1 este slo es cubierto sobre el ltimo UNI el cul es el V4.0. Esto ha sido ratificado y muchos fabricantes de switchs ATM ahora ya ofrecen soporte ABR. UBR: UBR opera en una base de mejor esfuerzo sin reservacin de

ancho de banda. La sealizacin usada para levantar y terminar llamadas es normalmente transmitida en UBR, como el trfico de un Emulador de Red de rea Local (LANE). GFR: GFR es un servicio nuevo el cul apenas se esta definiendo, este pretende brindar un mecanismo que liberar rfagas (como celdas). Si una celda esta perdida todas lo estn, lo cul es garantizado en una rfaga ms que en una celda.

54

ATM

Captulo. 1

Categora de Servicio QoS CBR VBR-RT VBR-NRT ABR UBR GFR Velocidad Constante de Bit Velocidad Variable de Bit Tiempo Real Velocidad Variable de Bit Tiempo No real Velocidad de Bit Disponible Velocidad de Bit No especificada Velocidad de Rfaga Garantizada

Fig. 3.2. Categora de Servicio QoS.

3.3. CLASES DE TRFICO ATM. El estndar ITU-T I.362 brinda las descripciones funcionales para las capas de adaptacin. Las clases de trfico se encuentran basadas en los siguientes parmetros: Si un vnculo con un timing es requerido entre la fuente y el destino. Si el trfico es CBR VBR. Si el trfico es orientado-a-conexin a no-conexin.

55

ATM

Captulo. 1

Clase A: Definida para datos tradicionalmente sncronos, tales como el contenido de un E1, circuitos de voz transmisin de video descomprimido. Clase B: Definida para video comprimido el cul requiere de un vnculo con el timing (regulacin de tiempo). Clase C: Definida para rfagas de datos tales como Frame Relay, X.25 transferencia de archivos muy grandes. Clase D: Incluye transmisin de datos como pueden ser mensajes SAP en una NetWare o un paquete ARP en TCP/IP. Adems de estos se encuentra definida una Clase X la cul est definida para UBR donde el tipo de trfico y requerimientos de timing son definidos por el usuario. Ms informacin con relacin a esto puede ser encontrada en documentacin ANSI (para clase Y).

Fig. 3.3. Clases de Servicio ATM.

56

ATM

Captulo. 1

3.4. PRINCIPIOS DE ADAPTACIN. Aunque el uso de la subcapa de convergencia (CS) es especificada para la capa de adaptacin, no todos los tipos de datos la requieren. La clase A (que es voz sncrona o video descomprimido) por ejemplo no necesita de esta subcapa. La capa superior de trfico de datos debe ser manipulada a travs de la subcapa de convergencia para asegurar que la transmisin terminal-a-terminal pueda ser tomada en una base de paquetes sin presentar una prdida de sesin. En adicin cada celda ATM debe ser llenada con datos, si la celda produce menos de 48 bytes, o si el volumen de datos no es divisible por un nmero entero de 48 bytes, entonces debe ser rellenada para ser adicionada. La subcapa de convergencia adiciona su propio rastreador y encabezado segmentacin y el reensamblado. En el diagrama abajo mostrado note que los encabezados adicionados estn dentro de la capa de adaptacin (AAL). Los actuales 5 bytes del encabezado de celda ATM no son adicionados hasta la capa ATM. antes de la

57

ATM

Captulo. 1

Fig. 3.4. Principios Generales de Adaptacin.

3.5. USOS DE LA CAPA DE ADAPTACIN. Como la capa de adaptacin es usada para adaptar trfico a un formato ATM, es necesario hacerlo a la entrada de la red ATM, una vez que el trfico es adaptado a un formato de celda ATM esta viaja a travs de la red en grupos de celdas, las cuales son conmutadas en la capa ATM de switches a travs de la ruta de la conexin ATM. Una vez que las celdas llegan a su destino, es necesario reensamblar el trfico de vuelta a el formato de la aplicacin original por lo que se puede decir que la capa de adaptacin es usada nuevamente a la salida de la red ATM.

58

ATM

Captulo. 1

Todos los switches por lo tanto requieren de una funcin de adaptacin, por ejemplo el trfico de sealizacin necesita ser interpretado por todos los switches; para interpretar el trfico de sealizacin entrante, el switch ATM necesita primeramente reensamblar el trfico de sealizacin y para esto requerir de una funcin de adaptacin. El switch sabe que el trfico que viene dentro de una conexin dada es trfico de sealizacin, como un reservado especial un valor VPI/VCI es usado. Similarmente todos los switches ATM necesitan interpretar el trfico de operacin y mantenimiento adems de la administracin del trfico.

Fig. 3.5. Uso de la Capa de Adaptacin.

59

ATM

Captulo. 1

3.6. CAPA DE ADAPTACIN AAL1. Datos Clase A (E1, DS1 y datos de otros circuitos de voz), la adaptacin AAL1 es para asegurar la integridad del timing entre el transmisor y el receptor final. Otra funcin es para portar o transmitir la recuperacin del reloj a el destino. La adaptacin adems brinda un mecanismo que detecta celdas perdidas e inserta un bit vigilante dentro del canal para asegurar que la informacin del timing no sea perdida. Operacin de AAL1: Para el formato de datos dentro de celdas, el canal de datos en la velocidad de operacin definida, simplemente corta en pedazos los 47 bytes. Estos pedazos ahora son llamados Unidades de Servicio de Datos (SDUs). Cada 47 bytes de SDU es precedido de 1 byte de encabezado resultando en un contenido de 48 bytes.

Fig. 3.6.a Capa de Adaptacin AAL1.

60

ATM

Captulo. 1

El byte de encabezado adiciona a cada 47 bytes de SDU dos partes: el campo de nmero de secuencia (SN) y el campo de proteccin del nmero de secuencia. El campo SN es entonces dividido en dos partes: el bit de indicacin de la subcapa de convergencia (CSI) el cul es normalmente puesto a 0 y tres bits para el nmero de secuencia. Estos ciclos atraviesan de 0 a 7 y regresan nuevamente a 0; esto es deseable para identificar celdas perdidas. Para asegurar la integridad del campo SN, este es protegido por el campo SNP, el cul cuenta con correccin de tres bits con un bit de paridad adicional.

Fig. 3.6.b Capa de Adaptacin AAL1.

61

ATM

Captulo. 1

3.7. CAPA DE ADAPTACIN AAL2. Se encarga de definir el transporte de el trfico VBR que es sensible al timing tal como VBR audio y video. AAL2 es nuevo y los datos los cuales deben ser soportados por el, tradicionalmente eran transmitidos por AAL5. Un problema con la utilizacin de AAL5 por lo tanto es la falta de parmetros de retardo; por contraste AAL2 es diseado inherentemente para soportar el trfico VBR para el cul el tiempo de liberacin es una consecuencia Una caracterstica de AAL2 es la habilidad para aceptar varios canales de trfico y multiplexarlos juntos. La manera de multiplexar la hace aceptando muestras y agregarles un encabezado pequeo a cada muestra, la funcin primaria aqu es adicionar un nmero de canal para identificar el canal de la capa mas alta. Una vez etiquetados, los bloques son transferidos a los contenidos de las celdas ATM, parte de esta transferencia es para agregar todava otro encabezado; el principal uso de este encabezado es identificar el comienzo y el flujo despus de un corto periodo de inactividad (uno de los canales puede mostrar una pantalla en blanco por un par de segundos y el canal puede producir que no halla salida).

62

ATM

Captulo. 1

Fig. 3.7.a Capa de Adaptacin AAL2.

3.7.1. ENCABEZADO INICIAL AAL2. Campos importantes del encabezado de paquetes inicial es el canal identificador (CID), el identificador de longitud (LI), y el campo de indicacin usuariousuario (UUI). Estos son definidos como a continuacin se muestra: Campo CID: Identifica el canal de usuario individual dentro de AAL2, y permite arriba de 248 usuarios individuales dentro de cada estructura AAL2. El campo CID es actualmente de 8 bits permitiendo tericamente un mximo de 255 usuarios individuales; por lo cul muchos valores CID son reservados para funciones de administracin y funciones futuras.

63

ATM

Captulo. 1

Campo LI: Identifica la longitud del contenido del paquete asociado con cada usuario individual y asegura transporte de el contenido de la variable. El valor de LI es uno menos que el contenido del paquete y tiene un valor por default de 45 octetos pudiendo llegar hasta 64 octetos. Campo UUI: Una aplicacin usual para este campo es para negociar un gran tamao de Unidad de Transferencia (MTU) para IP; esta funcin fue originada de la tercera generacin de estndar para telefona mvil. AAL2 es importante y ser fundamental para estndares UMTS. Portadoras de trfico IP tienen su mayor aplicacin en UMTS.

3.7.2. ENCABEZADO SECUNDARIO AAL2. Identifica la localizacin del inicio del siguiente paquete dentro del flujo, para fortalecerlo, el campo de inicio es protegido de errores por un bit de paridad (P) y la integridad de datos es protegida por el nmero de secuencia (SN).

64

ATM

Captulo. 1

Fig. 3.7.b Capa de Adaptacin AAL2.

3.8. CAPA DE ADAPTACIN AAL . Cuando empezamos a trabajar en la definicin de procesos de adaptacin esto hizo sentir que diferentes adaptaciones debieran ser requeridas para modos orientados a conexin y conexiones orientadas a datos; aunque despus de seis meses de trabajo los dos grupos de trabajo descubiertos han entregado resultados muy semejantes. Los dos grupos de trabajo subsecuentemente unieron fuerzas para desarrollar una simple adaptacin conocida como AAL3/4. Un paquete de datos completo por ejemplo un IP o un paquete IPX arriba de 64 kbit es tomado y encapsulado dentro de la subcapa de convergencia; rellenando de 0 a 3 octetos son adicionados para asegurar un alineamiento a 32 bits para simplificar su procesamiento.

65

ATM

Captulo. 1

La subcapa SAR entonces agrega un encabezado y rastreador para generar arriba de 48 bytes PDU los cuales tendrn un encabezado de 5 bytes agregados por la capa fsica para generar la celda de 53 bytes. En comparacin con la capa de adaptacin AAL5 esta adaptacin tiene 4 octetos ms por celda que la AAL5; esta efectivamente reduce la eficiencia de AAL3/4 (en comparacin con AAL5) por 4/48 que es aproximadamente un 8.3%.

3.8.1. RFAGAS AAL3/4. La estructura general de la subcapa de convergencia y capas SAR es como se muestra en el siguiente diagrama, como se puede ver AAL3/4 tiene relativamente un sobre-encabezado; en este caso 4 octetos son consumidos por el encabezado y campos rastreadores. Despus de substraer este sobre-encabezado el contenido ha sido reducido a 44 octetos. Aunque originalmente diseado para transportar todas las maneras de trafico de datos tradicionales, AAL3/4 fue visto como algo muy complejo de implementar e ineficiente debido a sus altos sobre-encabezados. Consecuentemente la mayora del trfico de datos es portado en AAL5. El rol principal de AAL3/4 hoy en da es en el servicio de transporte SMDS; SMDS es esencialmente una aplicacin y cree que SMDS migrar a el ms eficiente AAL5.

66

ATM

Captulo. 1

Fig. 3.8.a Capa de Adaptacin AAL .

3.8.2. AAL Y CAMPOS SAR. AAL3/4 CS

Tipo (Type): Indica la Unidad usada por el BA y los Campos de Longitud. Btag/Etag: Estos dos Tags son un valor numrico (el mismo valor), el cual ayuda a asegurar que es una simple unidad CS que ha sido recibida y no una unidad daada CS creada para unir dos unidades CS. Tamao BA (BA Size): Subcampo de longitud de la informacin de un usuario en el contenido CS.

67

ATM

Captulo. 1

Relleno (Pad): Agregacin de relleno para asegurar que la longitud total de el CS es divisible entre 4 (32 bits). Esta es una consideracin para simplificar el procesamiento por procesadores de 32 bits. Longitud (Length): Subcampo de la longitud de la informacin del usuario. Otros campos y subcampos son reservados para definiciones futuras.

AAL3/4 SAR

Tipo de Segmento (Segment Type): Indica si una celda es la primera (en el comienzo) de un mensaje (BOM), una continuacin de un mensaje (COM), o la ltima (al final) en un mensaje (EOM). Secuencia (Sequence): Indica la posicin en una convergencia PDU de un SAR PDU. MID: Este es un campo de multiplexacin ID, este puede ser usado para permitir la multiplexacin de varios canales de trfico dentro de una conexin simple; todas las celdas en una conexin tendrn por supuesto el mismo valor de VPI y VCI. Este campo extra es requerido para identificar un particular punto-terminal. Este servicio es de gran utilidad si la conexin es punto-multipunto.

68

ATM

Captulo. 1

Len: Esta es la longitud de los datos actuales en la ltima celda de un mensaje, la ltima celda de un mensaje puede no ser completamente llenada; nosotros la rellenaremos pero slo para alinearla a el lmite de 32bit en el CS. CRC: Una Correccin de Redundancia Cclica de 10-bit calculada sobre el SAR PDU.

Fig. 3.8.b Capa de Adaptacin AAL .

69

ATM

Captulo. 1

3.9. CAPA DE ADAPTACIN AAL5. AAL5 tiene significativamente mas bajos sobre-encabezados que AAL3/4 y es por lo tanto ampliamente adoptada, en prctica, la AAL2 ya no es usada y AAL3/4 es vista como una adaptacin compleja; slo AAL1 y AAL5 son ampliamente usadas. AAL1 es usada para trfico CBR y AAL5 para todas las dems: VBR, UBR y ABR. Formato de Rfagas AAL5 Mejor dicho las subcapas de mltiple convergencia de AAL3/4 y AAL5 simplemente toman el paquete de la capa de red y adicionan un rastreador simple. El campo de llenado sirve entonces para completar el PDU y que pueda ser entonces dividido entre un nmero entero de segmentos de 48-byte para cargarlo dentro de las celdas.

70

ATM

Captulo. 1

Fig. 3.9.a Capa de Adaptacin AAL5 (SEAL).

3.9.1. RASTREADOR AAL5. El rastreador (Trailer) AAL5 de 8-bytes consiste de: Dos campos de 1-byte los cuales no son usados. Un campo de longitud de 2-bytes el cul indica la longitud de los datos, no incluyendo el rastreador ni el llenado.

Un CRC de 4-bytes.

71

ATM

Captulo. 1

Fig. 3.9.b Capa de Adaptacin AAL5 (TRAILER).

3.9.2. TRANSMISIN AAL5. Con AAL5 no es un mtodo obvio de trabajar fuera, en donde las celdas representan el fin de un PDU y donde comienza el siguiente, para lograr esto, el campo PTI en el encabezado es usado. El bit 1 es puesto a 1 cuando la ltima celda representa que el PDU esta ensamblado y todas las dems celdas tienen el bit 0. Cuando el receptor observa el campo PTI con bit1 en 1 el asume que la siguiente celda con el mismo nmero de VPI/VCI ser la primera celda de un nuevo PDU.

72

ATM

Captulo. 1

Transmisin AAL5

AAL5 hace uso de el campo PTI en el encabezado de celdas ATM -Bit 1=1 Indica que esta transporta el rastreador AAL5

Fig. 3.9.c Transmisin AAL5.

73

ATM

Captulo. 1

4.1. FUNCIONES DE SEALIZACIN. Para establecer una conexin es esencial manejar algn tipo de sealizacin, las conexiones establecidas de esta forma son conocidos como circuitos virtuales de conmutacin (SVCs); adems es necesario adoptar un sistema de sealizacin el cul sea aceptado internacionalmente junto con un esquema de direccionamiento el cul opere en el cul operen de manera global.

El estndar ITU-T para sealizacin en redes pblicas ATM es conocido como Q.2931. El Foro ATM deriv dos estndares separados para esto; para redes privadas conocido como V3.0 y V3.1. V3.0 fue basado en un bosquejo del Q.2931 el cul fue inicialmente llamado Q.93b, y este a su vez fue basado en la especificacin ISDN Q.931. Desafortunadamente en la transicin entre Q.93b y Q.2931 un gran nmero de cambios fueron hechos para lograr que los mensajes de sealizacin fueran liberados. Este necesita de una versin separada del Foro de estndar ATM el cul fue liberado como V3.1; los dos estndares ATMF no son compatibles. Adems UNI 4.0 ha sido liberado, esto hace que la sealizacin ATMF se acerque cada vez ms a Q.2931. Toda la sealizacin dentro de ATM es transportada sobre un canal estndar reservado: VPI=0, VCI=5; donde la intencin de los operadores es que la funcin ATM podra trabajar en la mayora de los casos como una red telefnica normalmente lo hace.

74

ATM

Captulo. 1

Los SVCs no son reestablecidos ellos mismos en caso de una falla; todas las celdas ATM SVC viajan la misma ruta a travs de la sesin donde una prdida del circuito significar una prdida de conexin y por lo tanto necesitara de ser limpiada manualmente. La sealizacin es definida de manera independiente para usos a travs de una UNI (Q.2931, UNI 3.0, UNI 3.1, UNI 4.0) y para usos en una NNI para establecimiento de llamadas (PNNI).

Funciones de Sealizacin Una conmutacin de Circuitos Virtuales (SVCs) requiere el uso de estndares de sealizacin: - ITU-T Q.2931 - Foro ATM UNI V3.0, V3.1 y V4.0 Sealizacin para Interfases - UNI - NNI

Fig. 4.1. Funciones de Sealizacin.

4.2. FUNCIONES DE CONTROL DE SEALIZACIN. Igual que en un establecimiento de una conexin telefnica, a continuacin se muestran una serie que consta de varias fases:

75

ATM

Captulo. 1

Levantar la bocina (auricular). Esperar tono de marcacin. Marcar el nmero. Establecimiento de circuitos virtuales. Contestacin de una terminal distante. Transferencia de informacin. Limpiar sistema.

En ATM existen procedimientos similares: Antes que los datos puedan ser transmitidos, una ruta necesita ser establecida a travs de la red usando los mismos conceptos que para una llamada telefnica pero con muchos ms parmetros adicionales. Un requerimiento de establecimiento es generado por la fuente y propagado a travs de la red estableciendo una conexin entre el origen y el destino, despus los protocolos de enrutamiento se encargan de direccionar la llamada basada en un nmero de parmetros incluyendo la direccin destino, el ancho de banda requerido (hacia delante y hacia atrs) as como el QoS requerido. La llamada o la red pueden elegir entre aceptar o rechazar la llamada donde el establecimiento de llamada es basado en parmetros arreglados y un acercamiento para negociacin entre llamantes es muy limitado.

76

ATM

Captulo. 1

Funciones de Control de Sealizacin Establecimiento de un Circuito Virtual Reporte de Estado para un Circuito Virtual Mantenimiento a un Circuito Virtual Limpiado a un Circuito Virtual

Fig. 4.2. Funciones de Control de Sealizacin.

4.3. FORMATO DE DIRECCIONES.

AESA: El trmino correcto para una direccin ATM es Sistema de Direccin Terminal ATM (AESA: ATM End System Address). Aqu es importante saber que cuando usamos en esta modo la direccin no identificar una red SAP, slo direcciones NSAP son empleadas por lo que de acuerdo a esto es que son comnmente conocidas como direcciones NSAP. Formato de Direcciones DCC ATM: Indicador de Formato de Autoridad (AFI)=39. Cdigo de Conteo de Datos (DCC).

77

ATM

Captulo. 1

Formato de Direcciones ICD ATM: Indicador de Formato de Autoridad (AFI)=47. Designador de Cdigo Internacional (ICD). Formato de Direcciones E.164 NSAP encapsuladas: AFI=45. Formato de nmero E.164-An E.164. General: Dominio de Parte Especfica (DSP). Identificador de Sistema Terminal (ESI). Selector Sel.

Fig. 4.3. Formato de Direcciones.

78

ATM

Captulo. 1

4.4. ESTABLECIMIENTO DE LLAMADA. Un mensaje de establecimiento es enviado por el usuario llamante dentro de la red para iniciar una conexin, este despus pasa de la red al usuario destino para iniciar la conexin; asumiendo un establecimiento de llamada exitoso, el usuario destino responder con un mensaje de conexin. En el caso de el Antiguo Plan de Sistema Telefnico (POTS) la nica parte de informacin requerida para establecer una conexin fue la direccin del usuario destino; hasta hoy con ATM nosotros necesitamos especificar una lista de caractersticas que la red debe soportar, por ejemplo la calidad de servicio (QoS). Algunos de los parmetros en el mensaje de establecimiento son pertinentes para las redes mismas y otros para el destino. Por ejemplo de que forma la recuperacin de reloj necesita ser implementada en el destinatario.

79

ATM

Captulo. 1

Fig. 4.4. Establecimiento de Llamada.

4.5. LIBERACIN DE LLAMADA. El mensaje de liberacin puede ser enviado por cualquiera de los usuarios (llamante destino) para limpiar la conexin, si una de las partes limpia la conexin, entonces la red enviar un mensaje de limpiado a la parte opuesta. La red adems puede iniciar el limpiado, si por ejemplo en la misma ocurren fallas o por ausencia de trfico durante un periodo pre-determinado de tiempo. Un mensaje de liberacin puede ser liberada por cualquiera de los usuarios para terminar la llamada en cada etapa de la conexin. La liberacin eventualmente llegar a el otro extremo donde el usuario puede ser notificado y algn recurso local pueda ser liberado.

80

ATM

Captulo. 1

Fig. 4.5. Liberacin de Llamada.

4.6. CONEXIONES PUNTO-MULTIPUNTO. Las conexiones Multipunto son un servicio de las redes ATM; estas son usadas en todas las tcnicas LAN y sern un servicio muy importante de redes de transmisin encargadas de proveer la demanda de video. El proceso de un establecimiento de una conexin punto-multipunto comprende primeramente todos los establecimientos de conexiones punto-a-punto. Una vez que los destinos adicionales en un establecimiento inicial punto-a-punto pueden ser agregados, existen dos mecanismos que pueden ser usados aqu:

81

ATM

Captulo. 1

Enviar un requerimiento a la raz (el originador de el punto-a-punto original). Con sealizacin versin 4.0 libera un requerimiento LIJ (Leaf Iniated Join) unin de hojas iniciadas a la red.

En el caso de LIJ, la raz no necesariamente sabe de la existencia de la nueva pgina. Esto es problemtico: Como la hoja potencial identifica la conexin a la cul debe ser adicionada? La respuesta es por el uso de el identificador de conexin nico global (GUI) y un servidor el cul puede permitir GUIs para canales de celdas requeridos.

Fig. 4.6. Conexiones Punto-Multipunto.

82

ATM

Captulo. 1

4.7. CONTRATO DE TRFICO. El contrato de trfico es la suma de todos los parmetros requeridos para definir las caractersticas de una conexin, el contrato incluye una indicacin de cmo hace la red para verificar que el usuario no esta utilizando ms de los recursos solicitados en un tiempo establecido. El contrato consiste en una serie de requerimientos que son codificados para su transmisin en la red para el ingreso del switch a la red (esto incluye un valor de ancho de banda requerido y retardo). El establecimiento de llamada es el mensaje mas grande en la sealizacin ATM, por esto es en la etapa de establecimiento que la red pasar a travs de todos los detalles necesarios para la llamada, basados en el acuerdo de contrato de trfico. El mensaje de establecimiento transporta las direcciones ATM de 20 bytes de destino, adems de los parmetros de ancho de banda bsicos de adelanto y regreso, y la clase QoS. El mensaje de establecimiento puede adems transportar las direcciones fuente ATM. El algoritmo de Control de Admisin de Conexin (CAC) de el switch evaluar la red de acuerdo a lo requerido, antes permitiendo la conexin para proceder al establecimiento. Pasar la correccin local CAC no es garanta que la conexin ser exitosamente establecida.

83

ATM

Captulo. 1

El switch de ingreso retendr una copia de los parmetros pertinentes (tales como PCR, SCR y MBS) y usar esta informacin para revisar que la conexin se encuentre dentro de los lmites establecidos.

El Contrato de Trfico La direccin destino y el contrato de trfico forman la parte esencial de un establecimiento de llamada. El contrato de trfico entre el usuario y la red establece: - Un ancho de banda virtual reservado en cada uno de los avances o retrocesos de las direcciones. - La clase QoS para celdas en cada uno de los avances o retrocesos de las direcciones.

Fig. 4.7. El Contrato de Trfico.

4.8. SEALIZACIN UNI. Recordar que la Interfase Usuario-Red (UNI) es el punto entre el equipo ATM punto-terminal y el primer switch ATM, por lo que existen varias versiones de especificacin UNI definidas por el Foro ATM: UNI 2.0, UNI 3.0, UNI 3.1 y UNI 4.0 (tambin conocida como Sig 4.0). De estas especificaciones, UNI 2.0 solamente es capaz de soportar PVCs, mientras que las otras tres versiones son capaces de soportar hasta SVCs. Un importante punto a notar aqu es que la versin UNI 3.1 y versiones posteriores no son compatibles con la versin UNI 3.0.

84

ATM

Captulo. 1

Sealizacin UNI

El mensaje de establecimiento portar la fuente y la direccin ATM destino ms el ancho de banda y los parmetros QoS. -El mensaje de establecimiento de llamada es cortado usando AAL5 y enviado a un canal reservado (VPI=0, VCI=5).

Fig. 4.8. Sealizacin UNI.

4.9. FORMATO DE SEALIZACIN Q.2931. La sealizacin sobre ATM consiste de agrupar una variedad de bloques conteniendo la informacin necesaria, estos bloques edificados sern conocidos como elementos de informacin (IEs) y cada elemento tendr un estndar de 4bytes de encabezado seguido por el contenido (IE).

85

ATM

Captulo. 1

Establecimiento de Llamada:

Procedimiento de Llamada Conexin Reconocimiento de Conexin Establecimiento

Limpiado de Llamada: Liberacin Liberacin Completada Reiniciar Reconocimiento de Reinicio Miscelneos: Estado Estado Requerido Punto-Multipunto: Invitacin a Marcar Reconocimiento de Invitacin a Marcar Rechazo de Invitacin a Marcar Suprimir Invitacin a Marcar Reconocimiento de Rechazo a Marcar Un mensaje de establecimiento tiene arriba de 19 IEs de separacin aunque no todos son usados; elementos de informacin tales como parmetros AAL y nmero de invitacin a marcar son opcionales mientras que algunos como un descriptor de trfico, destino de llamada y limite permitido de ancho de banda son obligatorios.

86

ATM

Captulo. 1

Formato de Sealizacin Q.2931 La unidad de datos de sealizacin capa tres: - Encabezado estndar AAL tipo (5) Tipo de mensaje La estructura consiste de la construccin de bloques llamado elementos de informacin (IE). Ies son construidos por el tipo de mensaje y el tipo de servicio.

Fig. 4.9. Formato de Sealizacin Q.2931.

4.10. PAQUETES DE SEALIZACIN. El paquete de sealizacin es la Unidad de Intercambio entre las entidades de sealizacin, este paquete es transmitido en ambas direcciones a travs de la interfase, este paquete es elaborado de una serie de elementos de informacin. Un elemento de Informacin contiene valores para un parmetro simple o un grupo de parmetros por ejemplo un elemento pasa la Velocidad de Celda

87

ATM

Captulo. 1

Cumbre (PCR), Velocidad de Celda Sostenida (SCR) y el Tamao Mximo de Rfaga (MBS) dos grupos, uno por cada direccin.

Estos parmetros son claramente definidos mientras que otro IE porta la direccin de Invitacin a Marcar. Los paquetes de sealizacin son siempre reconocidos y estos pueden tener una longitud de miles de octetos con la finalidad de llenar plenamente los requerimientos del usuario.

Fig. 4.10. Paquete de Sealizacin.

88

ATM

Captulo. 1

89

ATM

Captulo. 1

5.1. NODOS DE CONMUTACIN ATM. El nodo de conmutacin bsico comprende un grupo e interfases para conexiones de entrada y salida, una estructura de conmutacin y un grupo de funciones de software.

Las tarjetas de interfase contienen un buffer para trfico de entrada y salida; este buffer acta como un organizador que selecciona cuales celdas van a ser puestas en los medios de salida. La estructura consiste de un componente de alta velocidad que mueve las celdas de la entrada del buffer a la salida del mismo. Las entidades de software incluye la pila de sealizacin; la pila de sealizacin incluye funciones para manejar sealizacin a travs de una Interfase UNI y NNI (para sealizacin inter-nodo pblica o privada). La administracin de software se encuentra aqu localizada: ILMI, configuracin de software y estructuras MIB. Otros elementos pueden estar presentes tal como un procesador de servicio que se encargar de abastecer otras funcionalidades por ejemplo un servidor orientado a conexin para manejar el establecimiento de conexiones SMDS).

90

ATM

Captulo. 1

Fig. 5.1. Conmutacin de Nodos ATM.

5.2. ARQUITECTURA DE UN SWITCH ATM. Bus Compartido (Shared Bus): La Arquitectura de un Switch Compartido brinda un bus de alta velocidad con un mecanismo arbitrario donde todo el trfico comparte un bus sencillo, tal que hace que el bus se comporte como un cuello de botella. Este diseo ha sido exitosamente puesto en prctica aunque algunos nuevos switches no tiendan a usar este diseo. En un principio esta era una buena opcin ya que los diseadores saban bastante acerca del diseo y construccin de las estructuras del bus. El diseo es para switches a pequea escala.

91

ATM

Captulo. 1

Punto Cruzado (Crosspoint): Este e ampliamente usado por el diseador donde otra vez la Teora de puntos cruzados fue bien definida antes de la llegada de ATM. La arquitectura no es escalable (el nmero de puntos cruzados crece exponencialmente con el nmero de entradas). Nosotros podemos encontrar este diseo en switches de pequeo y mediano tamao. Memoria Compartida (Shared Memory): Esta fue bien definida y ampliamente implementada en el diseo de su estructura; donde el diseo permite una fcil segregacin de diferentes clases de trfico. Conforme la memoria crece, el control crece en complejidad y en cerca de 65 mil celdas de almacenamiento estas necesitan ser removidas de 16 a 32-bits de procesamiento. El diseo trabaja bien y puede ser encontrado en switches de pequea y mediana escala. Delta: Diseo de Gran Escala que se mueve dentro de rutas paralelas y rutas internas que no son compartidas, el nombre genrico para esta estructura es Delta. Delta implica que la conmutacin es realizada en pequeos incrementos ya que la celda se propaga a travs de la estructura destino (puerto de salida) es definida en pequeos pasos incrementados; en esta configuracin la misma estructura de enrutamiento emerge en casos donde las celdas encuentran su propia forma de llegar al puerto de salida.

92

ATM

Captulo. 1

Fig. 5.2. Arquitectura de un switch ATM.

5.3. BUFFERS Y AMORTIGUAMIENTO. Un amortiguamiento puede ocurrir en la entrada, a la salida y dentro de la estructura, un amortiguador de entrada tiende a ser pequeo como la velocidad en la cual el trfico que llega es completamente definido por la velocidad de la interfase (velocidad de lnea). Un amortiguador de salida necesita ser mucho ms grande que varias entradas simultneamente direccionando celdas a una salida simple (nx155 no cabe dentro de 155). El amortiguamiento de salida puede ser implementado como parte de la arquitectura de la memoria compartida donde varias colas pueden ser creadas, una para cada categora de servicio.

93

ATM

Captulo. 1

Con varias colas se le puede dar preferencia a la cola CBR sobre la cola VBR; en casos extremos podemos proveer una cola por conexin e implementar un esquema muy bien definido de prioridades.

Fig. 5.3. Buffers y Amortiguamiento.

5.4. BLOQUEO / NO BLOQUEO. Bloqueo del Encabezado de Lnea (HOL): Esto puede ocurrir cuando una prioridad de trfico alta es introducida a una cola que ya contiene trfico de una prioridad baja, en este caso el trfico de prioridad alta tiene que esperar dado que el trfico de prioridad alta (por ejemplo trfico de voz) puede ser sensitivamente retrasado esto significa un problema.

94

ATM

Captulo. 1

Este posiblemente podra saltar la cola pero determinando el lugar correcto en la cola y subsecuentemente moviendo las otras celdas puede ser difcil en la prctica.