Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Ascensor Técnica Federico Santa María

Cargado por

Neryo Condori QDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Ascensor Técnica Federico Santa María

Cargado por

Neryo Condori QCopyright:

Formatos disponibles

Universidad Tcnica Federico Santa Mar e a Departamento de Informtica a Tarea No2 Arquitectura de Computadores El ascensor

Thomas Ernstorfer 2373501-6 Mauricio Acua n 2192008-8

Viernes 13 de Mayo del 2005

0.1.

Consideraciones (Supuestos)

Al recibir peticiones simultneas, el ascensor siempre mantiene el sena tido actual excepto cuando nadie llama al ascensor desde el piso en que el sentido indica. En este caso, el ascensor se queda en el estado en que est. a En caso de recibir peticiones simultneas, y el ascensor se encuentra a en un estado carente de sentido (piso 1 o piso 3), el ascensor se queda donde est. a Al no recibir peticiones, el ascensor se queda donde est. a El ascensor no distingue en la salida entre el Segundo Piso Subiendo y el Segundo Piso Bajando, para ambos valores, la salida es la misma.

0.2.

Diagrama de Estados

0.3.

Tabla de Transicin de Estados y Asignacin o o Secundaria

Se tienen cuatro estados, Primer Piso (1), Segundo Piso Bajando (2B), Segundo Piso Subiendo (2S) y Tercer Piso (3). Estos cuatro estados son representables usando dos bits, y por consiguiente, usando dos Flip-Flop, los que llamaremos X e Y . Para este circuito, usaremos Flip-Flop de tipo J-K. Se usarn tres entradas, las que sern los botones para llamar a a al ascensor de cada piso, es decir Botn del Primer Piso, Botn del Seo o gundo Piso y Botn del Tercer Piso. A cada una de estas entradas se les o nombrar a, b y c, respectivamente. La salida ser el piso en el que est el a a a ascensor, el que varia desde el uno al tres, por lo que queda representado usando dos bits, que llamaremos f y g. En s ntesis, la Asignacin Secundaria ser: o a Piso 1 2B 2S 3 X 0 0 1 1 Y 0 1 0 1

Luego, la tabla con las transiciones de estados y las salidas, con los estados representandos en funcin de X e Y , y las variables de entrada o ordenadas en cdigo gray (para mayor comodidad), ser: o a XY /abc 00 01 10 11 000 00 01 10 11 001 10 10 11 11 011 10 01 11 11 010 10 01 10 01 110 00 00 10 01 111 00 00 11 11 101 00 00 11 11 100 00 00 01 01 fg 01 10 10 11

0.4.

Mapas de Karnaugh de los Flip-Flop

n+1 J de X (XJ ) abc/XY 00 01 11 000 0 0 001 1 1 011 1 0 010 1 0 110 0 0 111 0 0 101 0 0 100 0 0 n+1 J de Y (YJ ) abc/XY 00 01 11 000 0 001 0 011 0 010 0 110 0 111 0 101 0 100 0 -

10 -

n+1 K de X (XK ) abc/XY 00 01 11 000 0 001 0 011 0 010 1 110 1 111 0 101 0 100 1 n+1 K de Y (YK ) abc/XY 00 01 11 000 0 0 001 1 0 011 0 0 010 0 0 110 1 0 111 1 0 101 1 0 100 1 0

10 0 0 0 0 0 0 0 1

10 0 1 1 0 0 1 1 1

10 -

0.5.

Mapas de Karnaugh de las Salidas

Salidas Y /X 0 1 0 01 10 1 10 11 Bit Y /X 0 1 f 0 0 1 1 1 1 Bit Y /X 0 1 g 0 1 0 1 0 1

0.6.

Minimizacin o

Se minimiza agrupando los bits 1 en el m nimo posible de subcubos adyacentes lo ms grandes posibles, como se muestra en los mapas de Karnaugh. a De los mapas de Karnaugh de los Flip-Flop (X e Y ), se tiene: An+1 = a b c + Y a b J An+1 = Y b c + a b c K 3

n+1 BJ = a c X + a c X + a b X = c X + a b X n+1 BK = a X + X a b c

Luego, de los Mapas de Karnaugh de las salidas (f y g), se obtiene: f =X +Y g =X Y +X Y =X Y

0.7.

Circuito

Finalmente, de las ecuaciones lgicas obtenidas en el punto anterior, es o posible construir el circuito minimizado. Aqu se presenta el circuito real izado en Klogic, mostrado por completo para mayor claridad:

También podría gustarte

- Electrónica Digital IIDocumento58 páginasElectrónica Digital IIDavid PiñaAún no hay calificaciones

- Angel Mendoza Circuitos DigitalesDocumento7 páginasAngel Mendoza Circuitos Digitalesalejandro montañaAún no hay calificaciones

- 13 ContadoresDocumento44 páginas13 ContadoresKarlita GaspitoAún no hay calificaciones

- Marco TeoricoDocumento20 páginasMarco TeoricoCarlos A. Pineda ChavarriaAún no hay calificaciones

- Informe Maquinas de EstadoDocumento10 páginasInforme Maquinas de EstadoEJ AlvarezAún no hay calificaciones

- T9024PU4E8LFL1V01Documento15 páginasT9024PU4E8LFL1V01cariasAún no hay calificaciones

- Mapa de KarnaughDocumento15 páginasMapa de Karnaughmaria lauraAún no hay calificaciones

- Mapas de KarnaughDocumento6 páginasMapas de KarnaughAlexandra ContrerasAún no hay calificaciones

- Sumativa N 3 Laborarrotio de Logica Digital Herms Chavez U.260621Documento18 páginasSumativa N 3 Laborarrotio de Logica Digital Herms Chavez U.260621Glenda Ureña de ChavezAún no hay calificaciones

- Tarea DomiciliariaDocumento26 páginasTarea DomiciliariaAndy1902100% (2)

- Maquinas SecuencialesDocumento34 páginasMaquinas SecuencialespapibelloAún no hay calificaciones

- Detector de secuencias 101 y 0110Documento16 páginasDetector de secuencias 101 y 0110Nicolas CastilloAún no hay calificaciones

- Implementación Del Flip-Flop Mediante Compuertas LógicasDocumento13 páginasImplementación Del Flip-Flop Mediante Compuertas LógicasArmandoAún no hay calificaciones

- Metodo de KarnaughDocumento24 páginasMetodo de KarnaughNora NaranjoAún no hay calificaciones

- Ac3 Cid GGDocumento11 páginasAc3 Cid GGGustavo Garmendia100% (1)

- Mapa de KarnaughDocumento14 páginasMapa de KarnaughMaria Jose Guedez SaldiviaAún no hay calificaciones

- Post-Laboratorio Flip-Flops Practica 6Documento17 páginasPost-Laboratorio Flip-Flops Practica 6Erick Manuel Molina ValeraAún no hay calificaciones

- Circuitos Lógicos, Tabla de La Verdad, Mapas de KarnaughDocumento27 páginasCircuitos Lógicos, Tabla de La Verdad, Mapas de KarnaughFRANCISCO MACUARANAún no hay calificaciones

- Diseño de Circuitos CombinatoriosDocumento11 páginasDiseño de Circuitos CombinatoriosKenneth CárdenasAún no hay calificaciones

- EJERCICiOS SECUENCIALESDocumento3 páginasEJERCICiOS SECUENCIALESanthony300Aún no hay calificaciones

- Contador BCD síncrono 4 bits con flip-flops J-KDocumento9 páginasContador BCD síncrono 4 bits con flip-flops J-KLuis Alberto Sota OrellanaAún no hay calificaciones

- U4 Diseno Circuitos Secuenciales SincronosDocumento13 páginasU4 Diseno Circuitos Secuenciales SincronosLizeth BenavidesAún no hay calificaciones

- Diego Romero-V26866833-Logica - Digital#03Documento16 páginasDiego Romero-V26866833-Logica - Digital#03Diego RomeroAún no hay calificaciones

- 1Documento15 páginas1Benjamin AlonsoAún no hay calificaciones

- Pract3mapas de KarnaughDocumento7 páginasPract3mapas de KarnaughChristian GonzalezAún no hay calificaciones

- Maquinas Secuenciales EjemplosDocumento12 páginasMaquinas Secuenciales EjemplosDanny Perez100% (1)

- TD - 5 - Mapa de KARNAUGHDocumento3 páginasTD - 5 - Mapa de KARNAUGHJean Franco Parisi Muñoz0% (1)

- Contador SincronoDocumento12 páginasContador SincronoJose Luis Tubon Condemaita100% (1)

- Flip FlopsDocumento13 páginasFlip FlopsDaniel GonzálezAún no hay calificaciones

- Códigos WincuplDocumento13 páginasCódigos WincuplDavid Griffin100% (1)

- Funciones cuadráticas: modelando situaciones realesDocumento23 páginasFunciones cuadráticas: modelando situaciones realesxiomaraAún no hay calificaciones

- Resumen Electronica 3Documento12 páginasResumen Electronica 3Laura C Caal HAún no hay calificaciones

- Puertas Lógicas Teoría y AscensorDocumento24 páginasPuertas Lógicas Teoría y AscensorEnrique Esteban Paillavil100% (1)

- Teoria Maquinas de EstadoDocumento28 páginasTeoria Maquinas de EstadoRonald Eder Chavez PalominoAún no hay calificaciones

- Ejercicios SecuencialesDocumento5 páginasEjercicios SecuencialesNaysha Stephanie AlvarezAún no hay calificaciones

- Guía 7 Plano InclinadoDocumento9 páginasGuía 7 Plano InclinadoMauro VelezAún no hay calificaciones

- Final 1Documento20 páginasFinal 1Hans A-LeonAún no hay calificaciones

- Ecuaciones de estado para circuitos secuencialesDocumento10 páginasEcuaciones de estado para circuitos secuencialesEdwin GómezAún no hay calificaciones

- Circuitos Secuenciales SincronosDocumento7 páginasCircuitos Secuenciales SincronosAndrea RamosAún no hay calificaciones

- Control de Maquinas Tarea 1Documento6 páginasControl de Maquinas Tarea 1kevin hernandezAún no hay calificaciones

- FSM Teoría Máquinas EstadoDocumento4 páginasFSM Teoría Máquinas EstadoManuel SilvaAún no hay calificaciones

- Presentacion Mapa de KarnaughDocumento13 páginasPresentacion Mapa de Karnaughcesar NogueraAún no hay calificaciones

- ElectroneumaticaDocumento6 páginasElectroneumaticaAndrezVasquezAún no hay calificaciones

- 06 Mapas de Karnaugh PDFDocumento92 páginas06 Mapas de Karnaugh PDFRobert Ruben Fuertes Veliz100% (1)

- Ejemplo de Dise PDFDocumento11 páginasEjemplo de Dise PDFPepe CamposAún no hay calificaciones

- Problemario 4Documento7 páginasProblemario 4Edward GiovannyAún no hay calificaciones

- Ensayo Sobre Logica SecuenciaDocumento21 páginasEnsayo Sobre Logica SecuenciaLuis Enrique Huh PucAún no hay calificaciones

- Circuitos Secuenciales: Los 4 tipos básicos de Flip-FlopsDocumento6 páginasCircuitos Secuenciales: Los 4 tipos básicos de Flip-FlopsHiram LoyaAún no hay calificaciones

- Latch NorDocumento3 páginasLatch NorRoberto SolorzanoAún no hay calificaciones

- Circuitos Logicos Ii ParcialDocumento30 páginasCircuitos Logicos Ii ParcialAlejandro DanielAún no hay calificaciones

- Teoría Geometría TerrenosDocumento4 páginasTeoría Geometría Terrenoschrismll100% (2)

- Problemas de Electronica DigitalDocumento8 páginasProblemas de Electronica DigitalManuel Alvariño TorresAún no hay calificaciones

- Guia 04 Deteccion Metales InductivoDocumento12 páginasGuia 04 Deteccion Metales InductivoNeryo Condori QAún no hay calificaciones

- Levitador Magnetico PDFDocumento73 páginasLevitador Magnetico PDFpr_alejAún no hay calificaciones

- 1550 Tutorial de ENGRANESDocumento8 páginas1550 Tutorial de ENGRANESjavier1437Aún no hay calificaciones

- BuenaDocumento14 páginasBuenaNeryo Condori QAún no hay calificaciones

- Financiamiento de La Seguridad SocialDocumento132 páginasFinanciamiento de La Seguridad SocialNeryo Condori Q0% (1)

- El Derecho A La Incapacidad Medica Desde La Perspectiva Del Voto 17971-2007 de La Sala ConstitucionalDocumento183 páginasEl Derecho A La Incapacidad Medica Desde La Perspectiva Del Voto 17971-2007 de La Sala ConstitucionalNeryo Condori QAún no hay calificaciones

- Controlador para Cuatro Motores Paso A PasoDocumento1 páginaControlador para Cuatro Motores Paso A PasoWilfredo GtAún no hay calificaciones

- "Adquisición de Audio Usando MATLAB" (Data Acquisition Toolbox) slidesDAQ - 2Documento36 páginas"Adquisición de Audio Usando MATLAB" (Data Acquisition Toolbox) slidesDAQ - 2e09081110Aún no hay calificaciones

- Contador SincronoDocumento4 páginasContador SincronoPablo AmurrioAún no hay calificaciones

- Circuitos ContadoresDocumento11 páginasCircuitos Contadoresdark_0Aún no hay calificaciones

- ServosDocumento3 páginasServoseeindustrialAún no hay calificaciones

- BuenaDocumento14 páginasBuenaNeryo Condori QAún no hay calificaciones

- LX1510Documento15 páginasLX1510Neryo Condori QAún no hay calificaciones

- Machineguarding WDocumento81 páginasMachineguarding WUriel CmaposAún no hay calificaciones

- Apuntes Calculo de TuberiasDocumento48 páginasApuntes Calculo de Tuberiasangelus7902Aún no hay calificaciones

- 6th Central Pay Commission Salary CalculatorDocumento15 páginas6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Pic 16 F 84Documento41 páginasPic 16 F 84David Riascos KAún no hay calificaciones

- Shopping Cart PDFDocumento1 páginaShopping Cart PDFNeryo Condori QAún no hay calificaciones

- Informe generador 01927-GEN-001 Andina CodelcoDocumento5 páginasInforme generador 01927-GEN-001 Andina CodelcoDomingo esteban perez ceballoAún no hay calificaciones

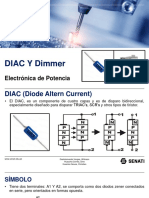

- Diac y DimmerDocumento13 páginasDiac y DimmerUlt DincyclistAún no hay calificaciones

- Colector de Campo - Topcon FC-5000Documento4 páginasColector de Campo - Topcon FC-5000Efrain CastroAún no hay calificaciones

- TEORIA y EJERCICIOS SOBRE LA BIOS - OdtDocumento3 páginasTEORIA y EJERCICIOS SOBRE LA BIOS - OdtgfelisfandosAún no hay calificaciones

- Redes EponDocumento10 páginasRedes EponOmar LlambaAún no hay calificaciones

- Microprocesadores (Silabo)Documento6 páginasMicroprocesadores (Silabo)Maldito SudacaAún no hay calificaciones

- Copia de Casos NecDocumento84 páginasCopia de Casos Necjuan david guerreroAún no hay calificaciones

- Antenas Con Reflectores ParabolicosDocumento15 páginasAntenas Con Reflectores ParabolicosPaul Tumbaco100% (1)

- Comparación Entre VHDL y Verilog - PEREYRA PELÁEZ OSCAR ABELDocumento3 páginasComparación Entre VHDL y Verilog - PEREYRA PELÁEZ OSCAR ABELanon_818776315Aún no hay calificaciones

- Guia 1. Compuertas LógicasDocumento5 páginasGuia 1. Compuertas LógicasDiegoErasoAún no hay calificaciones

- INVESTIGACION Circuito Timer 555Documento8 páginasINVESTIGACION Circuito Timer 555Miguel Angel Velazquez CamposAún no hay calificaciones

- Informe de Ensamblaje de PCDocumento6 páginasInforme de Ensamblaje de PCElvis Tarazona FloresAún no hay calificaciones

- Tarea 2Documento25 páginasTarea 2Alex Hernandez Santiago100% (1)

- Tabla de EscalamientoDocumento5 páginasTabla de EscalamientoHiram Cmi BautistaAún no hay calificaciones

- MegafoniaDocumento17 páginasMegafoniaEmmanuelSanzAún no hay calificaciones

- Cap 4 - Telefonia Planta Interna 2S PDFDocumento44 páginasCap 4 - Telefonia Planta Interna 2S PDFYhon DCAún no hay calificaciones

- ElectricidadDocumento21 páginasElectricidadJesus LobachevskiAún no hay calificaciones

- Tabulacion TicsDocumento14 páginasTabulacion TicsPablo Concha ArteagaAún no hay calificaciones

- Hoja Guía Práctica N. - 1Documento3 páginasHoja Guía Práctica N. - 1miguel10LAún no hay calificaciones

- Construcción de Segmentos de Red de Cobre Secundario PDFDocumento19 páginasConstrucción de Segmentos de Red de Cobre Secundario PDFJIJIJAún no hay calificaciones

- BioamplificadorDocumento28 páginasBioamplificadorHector Castillo CortesAún no hay calificaciones

- Normalización NTC para Empalme y Conectorizacion de Fibra Optica Transmision Om - OsDocumento16 páginasNormalización NTC para Empalme y Conectorizacion de Fibra Optica Transmision Om - OssergioAún no hay calificaciones

- 02 - Redes-Lan-Man-Wan-SanDocumento12 páginas02 - Redes-Lan-Man-Wan-SanArely Pierina Lizarraga OblitasAún no hay calificaciones

- Manual de Instruções Yamaha RX-V377 (2 Páginas)Documento13 páginasManual de Instruções Yamaha RX-V377 (2 Páginas)Renato Alves MarquesAún no hay calificaciones

- Los Transistores FET.Documento5 páginasLos Transistores FET.AlirioAún no hay calificaciones

- Codif-decodif-multi-demultiDocumento9 páginasCodif-decodif-multi-demultisergio alvarezAún no hay calificaciones

- Convertidores ADDocumento9 páginasConvertidores ADEmanuel CarrilloAún no hay calificaciones

- DSC PSP hs3032-3128 RFNAES 29010452R001Documento306 páginasDSC PSP hs3032-3128 RFNAES 29010452R001oscar_bcnAún no hay calificaciones

- Practica Circuito Integrador y Derivad PDFDocumento10 páginasPractica Circuito Integrador y Derivad PDFDennis GuamanAún no hay calificaciones

- Nom 185 Scfi 2017 - Dof - 2018 09 06Documento20 páginasNom 185 Scfi 2017 - Dof - 2018 09 06Gladio HSAún no hay calificaciones